МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ Федеральное государственное бюджетное образовательное учреждение высшего образования «Магнитогорский государственный технический университет им. Г.И. Носова»

(ФГБОУ ВО «МГТУ им. Г.И. Носова»)

УТВЕРЖДАЮ:

директор института Энергетики и автоматизированных систем

> С.И. Лукьянов 20 сентября 2017г.

## РАБОЧАЯ ПРОГРАММА ДИСЦИПЛИНЫ

# Основы проектирования электронной компонентной базы

Направление подготовки 11.03.04 «Электроника и наноэлектроника»

Направленность (профиль/ специализация) программы «Промышленная электроника»

Уровень высшего образования - бакалавриат

Программа подготовки – академический бакалавриат

Форма обучения Очная

Институт энергетики и автоматизированных систем Кафедра электроники и микроэлектроники Курс –4 Семестр –7 Рабочая программа составлена на основе ФГОС ВО по направлению 11.03.04 «Электроника и напоэлектроника», утвержденного приказом Министерства образования и науки Российской Федерации от 12.03.2015 г. N 218.

| Рабочая программа рассмотрена и одобрена на заседании кафедры "Электроники и<br>икроэлектроники" 7 сентября 2017 г., (протокол № 1).     |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Зав. кафедройС.И. Лукьянов                                                                                                               |

|                                                                                                                                          |

| Рабочая программа одобрена методической комиссией института Энергетики и<br>втоматизированных систем 20 сентября_2017 г. (протокол № 1). |

| ПредседательС.И. Лукьянов                                                                                                                |

|                                                                                                                                          |

| Рабочая программа разработана: <i>Швидченко Н.В.</i> , кандидатом технических наук,                                                      |

| оцентом кафедры Э и МЭ                                                                                                                   |

| Н.В. Швидченко                                                                                                                           |

| Рецензент:                                                                                                                               |

| Начальник отдела инновационных разработок ЗАО «КОНСОМ ГРУПП», канд. техн. наук                                                           |

|                                                                                                                                          |

# Лист регистрации изменений и дополнения

| №<br>п/<br>п | Раздел<br>программы | Краткое содержание<br>изменения/дополнения                                   | Дата.<br>№ протокола<br>заседания<br>кафедры | Подпись зав. кафедрой |

|--------------|---------------------|------------------------------------------------------------------------------|----------------------------------------------|-----------------------|

| 1.           | 8                   | Актуализация учебно - методического и информационного обеспечения лисциплины | 06.09.2018 г.<br>протокол №1                 | Po                    |

| 2.           | 8                   | Актуализация учебно - методического и информационного обеспечения дисциплины | 05.09.2019 г.<br>протокол №1                 | Po                    |

| 3.           | 8                   | Актуализация учебно - методического и информационного обеспечения дисциплины | 31.08.2020 г.<br>протокол №1                 | Do                    |

#### 1 Цели освоения дисциплины

Целями освоения дисциплины «Основы проектирования электронной компонентной базы» являются изучение современных методов и маршрутов проектирования электронной компонентной базы, средств и способов автоматизации процесса проектирования, а также изучение способов представления адекватной современному уровню знаний научной картины мира на основе знания основных положений, законов и методов естественных наук и математики, выполнять расчет и проектирование электронных приборов, схем и устройств различного функционального назначения с использованием средств автоматизации проектирования, разрабатывать проектную и техническую документацию, оформлять законченные проектно-конструкторские работы.

# 2 Место дисциплины в структуре ООП подготовки бакалавра (магистра, специалиста)

Дисциплина «Основы проектирования электронной компонентной базы» входит в базовую часть блока 1 образовательной программы.

Изучение данной дисциплины базируется на результатах изучения дисциплин математического и естественно-научного цикла, в том числе математики, физики, информатики, а также дисциплин профессионального цикла: «Теоретические основы электротехники», «Физические основы электроники», «Схемотехника».

Студент, приступивший к изучению дисциплины «Проектирование и технология электронной компонентной базы» должен:

#### знать:

- основные понятия и методы математического анализа, линейной алгебры, теории дифференциальных уравнений и элементов теории уравнений математической физики, теории функций комплексной переменной, теории вероятностей и математической статистики, дискретной математики, математических методов решения профессиональных задач;

- фундаментальные законы природы и основные физические законы в области механики, термодинамики, электричества и магнетизма, оптики и атомной физики;

- теоретические основы строения вещества, зависимость химических свойств веществ от их строения; основные закономерности протекания химических и физико-химических процессов;

- основы теории электрических и магнитных, пассивных и активных, линейных и нелинейных цепей с сосредоточенными и распределенными параметрами; эквивалентные схемы активных элементов; методы анализа частотных и переходных характеристик;

#### уметь:

- применять математические методы, физические и химические законы для решения практических задач;

- применять методы и средства измерения физических величин;

- проводить анализ цепей при постоянном и синусоидальном воздействии, а также при воздействии сигналов произвольной формы, импульсных сигналов;

#### владеть:

- -методами решения дифференциальных и алгебраических уравнений, дифференциального и интегрального исчисления, аналитической геометрии, теории вероятностей и математической статистики, математической логики, функционального анализа;

- -навыками практического применения законов физики и химии;

- -современными программными средствами подготовки конструкторско-

технологической документации;

- методами анализа переходных процессов в линейных и нелинейных цепях.

Освоение студентами дисциплины «Основы проектирования электронной компонентной базы» необходимо при изучении дисциплины «Основы технологии электронной компонентной базы».

# 3 Компетенции обучающегося, формируемые в результате освоения дисциплины (модуля):

В результате освоения дисциплины (модуля) «Основы проектирования электронной компонентной базы» обучающийся должен обладать следующими компетенциями:

| Структурный эле-<br>мент<br>компетенции                                                                                                                                                                                    | Планируемые результаты обучения                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                            | представлять адекватную современному уровню знаний науча основе знания основных положений, законов и методов естегематики                                                                                                                                                                                                                                                                             |  |  |  |

| Знать                                                                                                                                                                                                                      | <ul> <li>классификацию современной электронной компонентной базы;</li> <li>сферу применения современной электроники;</li> <li>перспективные направления современной электроники;</li> </ul>                                                                                                                                                                                                           |  |  |  |

| Уметь:                                                                                                                                                                                                                     | <ul> <li>классифицировать схемы и устройства в соответствии с современной классификацией электронной компонентной базой;</li> <li>осуществлять выбор элементной базы при проектировании электронных приборов, схем и устройств в соответствии со сферой применения;</li> </ul>                                                                                                                        |  |  |  |

| Владеть:                                                                                                                                                                                                                   | <ul> <li>навыками работы с информационными базами данных совре-<br/>менной электронной компонентной базы, справочными мате-<br/>риалами;</li> </ul>                                                                                                                                                                                                                                                   |  |  |  |

| ПК-5 готовность выполнять расчет и проектирование электронных приборов, схем и устройств различного функционального назначения в соответствии с техническим заданием с использованием средств автоматизации проектирования |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Знать                                                                                                                                                                                                                      | <ul> <li>основные этапы проектирования электронных приборов, схем и устройств. Концепцию сквозного проектирования;</li> <li>элементную базу современной электроники. Основные САПР сквозного проектирования электронных приборов, схем и устройств;</li> <li>основные методы проектирования электронных систем (схемотехническое проектирование, на основе HDL, системное проектирование);</li> </ul> |  |  |  |

| Уметь:                                                                                                                                                                                                                     | <ul> <li>анализировать техническое задание, пользоваться проектной документацией;</li> <li>осуществлять выбор элементной базы при проектировании электронных приборов, схем и устройств в соответствии с техническим заданием. Осуществлять выбор необходимых САПР;</li> <li>проектировать электронные приборы схемы и устройства на</li> </ul>                                                       |  |  |  |

| Структурный эле-<br>мент<br>компетенции | Планируемые результаты обучения                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | основе различных методов проектирования (схемотехниче-<br>ское, на основе HDL, системное проектирование) с использо-<br>ванием САПР;                                                                                                                                                                                              |

| Владеть:                                | <ul> <li>навыками работы с проектной документацией, информационными базами данных об отечественных и зарубежных компонентах;</li> <li>навыками работы с основными САПР электронных приборов, схем и устройств;</li> <li>основными методами проектирования (схемотехническое, на основе HDL, системное проектирование);</li> </ul> |

|                                         | <br>нарабатывать проектную и техническую документацию,<br>нные проектно-конструкторские работы                                                                                                                                                                                                                                    |

| Знать                                   | <ul> <li>Основные формы представления проектной документации в соответствии с требованиями ЕСКД;</li> <li>Стандартные опции САПР для формирования проектной документации;</li> <li>Правила организации многоуровневой проектной документации для сложных проектов;</li> </ul>                                                     |

| Уметь                                   | <ul> <li>анализировать техническое задание на проект, пользоваться проектной документацией;</li> <li>использовать стандартные опции САПР для формирования проектной документации;</li> <li>разрабатывать многоуровневую проектную документацию для сложных проектов с помощью САПР;</li> </ul>                                    |

| Владеть                                 | <ul> <li>навыками работы с проектной документацией;</li> <li>стандартными опциями САПР для формирования проектной документации;</li> <li>навыками работы с различными САПР для осуществления документооборота между ними;</li> </ul>                                                                                              |

# 4 Структура и содержание дисциплины (модуля)

Общая трудоемкость дисциплины составляет 3 зачетных единицы, 108 часов, в том числе:

- -контактная работа 37 акад. часов:

- аудиторная 36 акад. часов;

- внеаудиторная 1 акад. час;

- -самостоятельная работа 71 акад. час.

| Раздел<br>дисциплины                                                                                                                                                                                                       | Семестр | Ауди<br>на<br>конта<br>раб<br>(в ан<br>час | ктная<br>ота<br>кад. | Самостоятельная работа (в акад. часах) | Вид самостоятельной работы                                                      | Формы теку-<br>щего контроля<br>успеваемости и<br>промежуточной<br>аттестации | Код и структурный<br>элемент<br>компетенции |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------|----------------------|----------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------|

| 1. Современная электронная компонентная база. Классификация. Область применения                                                                                                                                            | 7       | 2                                          |                      | 10                                     | Самостоятель-<br>ное изучение<br>учебной литера-<br>туры                        | Контрольная<br>работа                                                         | ПК-5 –<br>зув                               |

| 2. Проектирование электронной компонентной базы: основные этапы и уровни проектирования.                                                                                                                                   | 7       | 4                                          |                      | 10                                     | Самостоятельное изучение учебной литературы                                     | Контрольная<br>работа                                                         | ПК-5 –<br>зув<br>ПК-6 –<br>зув              |

| 3. Системы автоматизированного проектирования (САПР). Обзор САПР для различных уровней проектирования. Языки описания аппаратуры HDL. Сквозное проектирование цифровых устройств на основе ПЛИС в САПР ISE WebPACK Xilinx. | 7       | 4                                          | 8/4                  | 20                                     | Самостоятельное изучение учебной литературы; Подготовка к практическим занятиям | Контрольная<br>работа                                                         | ПК-5 –<br>зув<br>ПК-6 –<br>зув              |

| 4. Виды моделирования и типы моделей на различных этапах проектирования. Использование VHLDи SPICE-моделей. Моделирование работы цифровых устройств с помощью встроенного в САПР ISE WebPACK симулятора Isim.              | 7       | 4                                          | 5/2                  | 20                                     | Самостоятельное изучение учебной литературы; Подготовка к практическим занятиям | Контрольная<br>работа                                                         | ПК-5 –<br>зув<br>ПК-6 –<br>зув              |

| 5. Разработка проектной документации. Конфигурирование ПЛИС с помощью встроенной в САПР ISE WebPACK программы Impact. Тестирование готовых устройств. JTAG-интерфейс.                                                      | 7       | 4                                          | 5/2                  | 11                                     | Самостоятельное изучение учебной литературы; Подготовка к практическим занятиям | Контрольная<br>работа                                                         | ПК-5 –<br>зув<br>ПК-6 –<br>зув              |

| Итого по дисциплине                                                                                                                                                                                                        |         | 18                                         | 18/<br>8             | 71                                     |                                                                                 | Зачёт                                                                         |                                             |

#### 5 Образовательные технологии

Лекционные занятия по дисциплине «Основы проектирования электронной компонентной базы» проводятся в традиционной форме с использованием мультимедийного оборудования. Практические занятия проходят как в традиционной форме, так и в интерактивной форме, где студентам заранее предлагается ознакомиться с информацией по теме занятия для подготовки вопросов преподавателю, таким образом, практическое занятие проходит по типу «вопросы—ответы—дискуссия». На всех практических занятиях также применяются элементы занятия-визуализации, за счет представления части материала с помощью заранее подготовленных презентаций, слайдов с помощью мультимедийного оборудования.

Теоретический материал, освоенный студентами самостоятельно, закрепляется на практических занятиях, на которых выполняются индивидуальные и групповые задания по пройденной теме. Часть практических занятий проводится в виде традиционных семинаров с целью более глубокого и полного усвоения теоретического материала по данной теме. Для этого студентам предлагается готовить доклады по рассматриваемой теме с дальнейшим обсуждением в ходе практического занятия (учебных дискуссий). На практических занятиях также применяются метод контекстного обучения, работы в команде и метод саse-study, позволяющие усвоить учебный материал путём выявления связей между конкретным знанием и его применением, а также анализа конкретных ситуаций и поиска решений в группе студентов. Защита результатов практических заданий проходит в виде диалога преподавателя и студента, преподавателем задаются контрольные вопросы с целью выяснения глубины знаний студента по данному разделу, при этом пробелы в знаниях студента восполняются дополнительными пояснениями, комментариями преподавателя.

В качестве оценочных средств на протяжении семестра используются контрольные работы. Самостоятельная работа студентов заключается в проработке материала при подготовке к практическим занятиям.

#### 6 Учебно-методическое обеспечение самостоятельной работы студентов

По дисциплине «Основы проектирования электронной компонентной базы» предусмотрена аудиторная и внеаудиторная самостоятельная работа обучающихся.

Аудиторная самостоятельная работа студентов предполагает решение контрольных задач на практических занятиях.

Примерные аудиторные контрольные работы (АКР):

АКР №1 «Современная электронная компонентная база. Классификация. Область применения»:

- 1. Классификация электровакуумных электронных приборов.

- 2. Сфера применения электровакуумных приборов.

- 3. Перспективы применения электровакуумных приборов.

- 4. Какие элементы входят в модель прибора вакуумной электроники.

- 5. Какие электронно-лучевые приборы вы знаете?

- 6. Что такое полупроводниковый электронный прибор?

- 7. Классификация полупроводниковых приборов.

- 8. Сфера применения полупроводниковых приборов.

- 9. Какие полупроводниковые приборы вы знаете?

- 10. Перспективы применения полупроводниковых приборов.

- 11. Элементная база оптоэлектроники.

- 12. Сфера применения оптоэлектроники

- 13. Что такое интегральная схема?

- 14. Классификация интегральных схем?

- 15. Что значит технологическая норма интегральной схемы?

- 16. Элементная база интегральных схем.

- 17. Что такое заказная ИС

- 18. Что такое полузаказная ИС?

- 19. Что представляет собой базовый матричный кристалл?

- 20. Что такое программируемая логическая интегральная схема?

- 21. Что такое «система на кристалле»?

- 22. Что такое логический элемент ИС?

- 23. Что такое логическая ИС комбинационного типа?

- 24. Что такое логическая ИС последовательностного типа?

- 25. Какие типы логических ячеек (логики) вы знаете?

АКР №2 «Проектирование электронной компонентной базы: основные этапы и уровни проектирования»:

- 1. Перечислите основные этапы производства ИС

- 2. Что включает в себя спецификация на разрабатываемую ИС

- 3. Какова иерархия проектирования СБИС.

- 4. Что такое кремниевый уровень проектирования. Какие примитивы применяются на данном уровне.

- 5. Что такое транзисторный уровень проектирования. Какие примитивы применяются на данном уровне.

- 6. Что такое вентильный уровень проектирования. Какие примитивы применяются на данном уровне.

- 7. Что такое регистровый уровень проектирования. Какие примитивы применяются на данном уровне.

- 8. Что такое процессорный уровень проектирования. Какие примитивы применяются на данном уровне.

- 9. Что такое системный уровень проектирования. Какие примитивы применяются на данном уровне.

- 10. В чём заключается принцип управления сложностью (абстрагирование) при разработке электроники.

- 11. Какова современная инфраструктура производства ИС.

- 12. Что представляют собой кремниевые фабрики.

- 13. Что такое ІР-блок.

- 14. Классификация ІР-блоков

- 15. В чём отличие программных ІР-блоков от аппаратных ІР-блоков.

- 16. Что представляют собой топологические ІР-блоки.

- 17. Этапы проектирования заказной ИС.

- 18. Этапы проектирования ИС на стандартных ячейках.

- 19. Этапы проектирования схемы на базе ПЛИС.

АКР №3 «Системы автоматизированного проектирования (САПР). Обзор САПР для различных уровней проектирования. Языки описания аппаратуры **HDL**. Сквозное

проектирование цифровых устройств на основе ПЛИС в САПР ISE WebPACK Xilinx»:

- 1. Что такое язык описания аппаратуры HDL.

- 2. Каковы преимущества разработки схемы на базе HDL по сравнению со схемотехническим способом.

- 3. Что такое логический синтез схемы.

- 4. Какие САПР разработки ИС вы знаете?

- 5. Какие САПР для разработки схем на базе ПЛИС вы знаете?

- 6. Логический синтез ИС на стандартных ячейках.

- 7. Логический синтез схем на ПЛИС.

- 8. Что такое критический путь цифровой схемы?

- 9. Какие языки описания аппаратуры вы знаете?

- 10. Чем отличаются синтезируемые структуры языка HDL от несинтезируемых?

- 11. Какими способами можно повысить быстродействие цифровой схемы?

- 12. В чём заключается компромисс площадь кристалла/быстродействие?

- 13. Что такое синхронная цифровая схема?

- 14. Что включает в себя описание интерфейса (entity declaration) в языке VHDL.

- 15. Какие значения поддерживает тип данных **STD\_LOGIC** в языке VHDL.

- 16. Чем отличается тип данных **STD\_LOGIC** от **STD\_LOGIC\_VECTOR** в языке VHDL.

- 17. В чём отличие объекта **port** от объекта **signal** в языке VHDL.

- 18. Какие значения поддерживает тип данных **unsigned** в языке VHDL. Является ли данный тип синтезируемым?

- 19. Какие значения поддерживает тип данных **integer** в языке VHDL. Является ли данный тип синтезируемым?

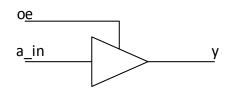

- 20. Является ли высокоимпедансное состояние **Z** синтезируемым в языке VHDL? Если да, то какая схема синтезируется?

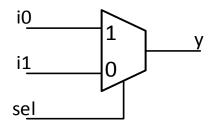

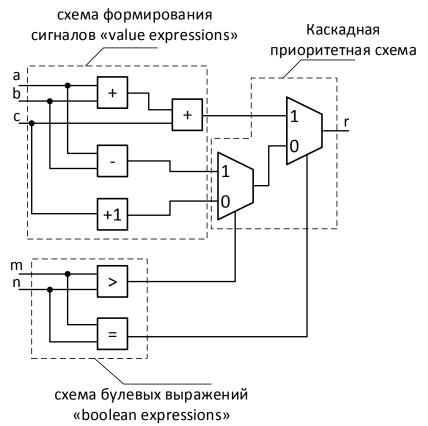

- 21. Каков синтаксис структуры «присваивание по условию» (**conditional signal assignment**) в языке VHDL. В Какую схему данная структура синтезируется?

- 22. Каков синтаксис структуры «Присваивание по выбору» (selected signal assignment) в языке VHDL. В Какую схему данная структура синтезируется?

- 23. Каков синтаксис оператора **if** в языке VHDL. В Какую схему данная структура синтезируется?

- 24. Каков синтаксис оператора **case** в языке VHDL. В Какую схему данная структура синтезируется?

- 25. Для чего в языке VHDL используется структура **process**?

- 26. Разработать одноразрядную схему сравнения на вентильном уровне на языке VHDL.

- 27. Разработать на языке VHDL схему дешифратора 2 в 4.

- 28. Разработать на языке VHDL схему преобразователя двоичного кода в семисегментный.

- 29. Разработать модуль на VHDL, вычисляющий четырехвходовую функцию XOR (исключающее ИЛИ).

- 30. Разработать на языке VHDL схему 4-х разрядного счётчика.

- 31. Разработать на языке VHDL схему 4-х разрядного сумматора чисел со знаком.

- 32. Для чего применяется generic в языке VHDL.

- 33. Что значит параметризованная схема?

- 34. Разработать на языке VHDL схему 8-и разрядного регистра.

- 35. Разработать на языке VHDL схему сдвигового регистра с параллельной загрузкой.

- 36. Разработать на языке VHDL схему конечного автомата для детектирования переднего фронта сигнала.

АКР №3 «Виды моделирования и типы моделей на различных этапах проектирования. Использование **VHLD**- и **SPICE**-моделей. Моделирование работы цифровых устройств с помощью встроенного в САПР **ISE WebPACK** симулятора **Isim**»:

- 1. Что такое среда тестирования (testbench).

- 2. Что такое среда тестирования с самопроверкой?

- 3. Что такое функциональное моделирование?

- 4. Уровни верификации СБИС.

- 5. Назначение функциональных блоков stimulus, checker и monitor в среде тестирования?

- 6. Что такое рандомизация тестовых воздействий (stimulus)

- 7. Что такое ограниченная (constrained) рандомизация тестовых воздействий

- 8. Чем отличается кодовое покрытие от функционального покрытия при верификации схемы?

- 9. Что такое метрика при верификации схемы? Какие метрики используются?

- 10. Что такое эмуляция схемы?

- 11. Что такое формальная проверка эквивалентности на этапе синтезирования схемы?

- 12. Что такое временное моделирование схемы?

- 13. Написать testbench на VHDL с самопроверкой для одноразрядной схемы сравнения.

- 14. Написать testbench на VHDL для схемы дешифратора 2 в 4.

- 15. Написать testbench на VHDL для схемы преобразователя двоичного кода в семисегментный.

- 16. Написать testbench на VHDL с самопроверкой для 4-х разрядной схемы XOR (исключающее ИЛИ).

- 17. Написать testbench на VHDL для схемы 4-х разрядного счётчика.

- 18. Написать testbench на VHDL для схемы 4-х разрядного сумматора чисел со знаком

- 19. Написать testbench на VHDL для схемы 8-и разрядного регистра.

- 20. Написать testbench на VHDL для схемы сдвигового регистра с параллельной загрузкой.

- 21. Написать testbench на VHDL для схемы детектирования переднего фронта сигнала.

АКР №5 «Разработка проектной документации. Конфигурирование ПЛИС с помощью встроенной в САПР **ISE WebPACK** программы **Impact**. Тестирование готовых устройств. JTAG-интерфейс»:

- 1. Что такое имплементация?

- 2. Каковы основные рекомендации по размещению блоков на кристалле?

- 3. Что такое слой металлизации в ИС?

- 4. Что такое трассировка?

- 5. Применение манхэтоновской геометрии при трассировке.

- 6. Что такое физическая верификация ИС?

- 7. Что такое DRC проверка?

- 8. Что такое ERC проверка?

- 9. Что такое LVS проверка?

- 10. Что такое GDSII формат?

- 11. Что такое JTAG тестирование?

- 12. Что такое цепочка тестирования?

- 13. Что такое встроенное самотестирование BIST?

- 14. Встроенное самотестирование памяти.

- 15. Что такое периферийное сканирование?

- 16. Реализовать одноразрядную схему сравнения на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 17. Реализовать схему дешифратора 2 в 4 на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 18. Реализовать схему преобразователя двоичного кода в семисегментный на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 19. Реализовать четырехвходовую функцию XOR (исключающее ИЛИ) на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 20. Реализовать схему 4-х разрядного счётчика на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 21. Реализовать схему 4-х разрядного сумматора чисел со знаком на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 22. Реализовать схему 8-и разрядного регистра на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 23. Реализовать схему сдвигового регистра с параллельной загрузкой на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- 24. Реализовать схему детектирования переднего фронта сигнала на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

Внеаудиторная самостоятельная работа обучающихся осуществляется в виде изучения литературы по соответствующему разделу с проработкой материала.

#### 7 Оценочные средства для проведения промежуточной аттестации

а) Планируемые результаты обучения и оценочные средства для проведения промежуточной аттестации:

| Структурный элемент компетенции                                              | Планируемые результаты обучения | Оценочные средства |  |  |

|------------------------------------------------------------------------------|---------------------------------|--------------------|--|--|

| ОПК-1 способность представлять адекватную современному уровню знаний научную |                                 |                    |  |  |

|               | картину мира на основе знания основных положений, законов и методов естественных |                                                                                              |  |  |  |

|---------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| наук и матема |                                                                                  |                                                                                              |  |  |  |

| Знать         | – классификацию современной элек-                                                | – Классификация электровакуумных                                                             |  |  |  |

|               | тронной компонентной базы;                                                       | электронных приборов.                                                                        |  |  |  |

|               | – сферу применения современной                                                   | – Сфера применения электровакуум-                                                            |  |  |  |

|               | электроники;                                                                     | ных приборов.                                                                                |  |  |  |

|               | – перспективные направления со-                                                  | – Перспективы применения электро-                                                            |  |  |  |

|               | временной электроники;                                                           | вакуумных приборов.                                                                          |  |  |  |

|               |                                                                                  | – Какие элементы входят в модель                                                             |  |  |  |

|               |                                                                                  | прибора вакуумной электроники.                                                               |  |  |  |

|               |                                                                                  | – Какие электронно-лучевые приборы                                                           |  |  |  |

|               |                                                                                  | вы знаете?                                                                                   |  |  |  |

|               |                                                                                  | <ul> <li>- Что такое полупроводниковый</li> </ul>                                            |  |  |  |

|               |                                                                                  | электронный прибор?                                                                          |  |  |  |

|               |                                                                                  | – Классификация полупроводниковых                                                            |  |  |  |

|               |                                                                                  | приборов.                                                                                    |  |  |  |

|               |                                                                                  | – Сфера применения полупроводнико-                                                           |  |  |  |

|               |                                                                                  | вых приборов.                                                                                |  |  |  |

|               |                                                                                  | – Какие полупроводниковые приборы                                                            |  |  |  |

|               |                                                                                  | вы знаете?                                                                                   |  |  |  |

|               |                                                                                  | – Перспективы применения полупро-                                                            |  |  |  |

|               |                                                                                  | водниковых приборов.                                                                         |  |  |  |

|               |                                                                                  | <ul><li>Элементная база оптоэлектроники.</li></ul>                                           |  |  |  |

|               |                                                                                  | <ul><li>Сфера применения оптоэлектроники</li></ul>                                           |  |  |  |

|               |                                                                                  | <ul><li>- Сфера применения оптоэлектроники</li><li>- Что такое интегральная схема?</li></ul> |  |  |  |

|               |                                                                                  | -                                                                                            |  |  |  |

|               |                                                                                  | – Классификация интегральных схем?                                                           |  |  |  |

|               |                                                                                  | – Что значит технологическая норма                                                           |  |  |  |

|               |                                                                                  | интегральной схемы?                                                                          |  |  |  |

|               |                                                                                  | – Элементная база интегральных                                                               |  |  |  |

|               |                                                                                  | схем.                                                                                        |  |  |  |

| Уметь:        | – классифицировать схемы и                                                       | – Что такое заказная ИС                                                                      |  |  |  |

| J MCTB.       | устройства в соответствии с со-                                                  | <ul><li>- Что такое полузаказная ИС?</li></ul>                                               |  |  |  |

|               | временной классификацией элек-                                                   | — Что представляет собой базовый                                                             |  |  |  |

|               | тронной компонентной базой;                                                      | матричный кристалл?                                                                          |  |  |  |

|               | <ul><li>– осуществлять выбор элементной</li></ul>                                | — Что такое программируемая логи-                                                            |  |  |  |

|               | базы при проектировании электрон-                                                | - что такое программируемая логи-<br>ческая интегральная схема?                              |  |  |  |

|               | ных приборов, схем и устройств в                                                 | _                                                                                            |  |  |  |

|               | соответствии со сферой примене-                                                  | – Что такое «система на кристал-                                                             |  |  |  |

|               | ния;                                                                             | ne»?                                                                                         |  |  |  |

|               | ,                                                                                | — Что такое логический элемент ИС?                                                           |  |  |  |

|               |                                                                                  | – Что такое логическая ИС комбина-                                                           |  |  |  |

|               |                                                                                  | ционного типа?                                                                               |  |  |  |

|               |                                                                                  | – Что такое логическая ИС последо-                                                           |  |  |  |

|               |                                                                                  | вательностного типа?                                                                         |  |  |  |

|               |                                                                                  | – Какие типы логических ячеек (логи-                                                         |  |  |  |

|               |                                                                                  | ки) вы знаете?                                                                               |  |  |  |

| Владеть:      | – навыками работы с информацион-                                                 | <ul> <li>Каких производителей современной</li> </ul>                                         |  |  |  |

| эладегь.      | ными базами данных современной                                                   | электроники вы знаете?                                                                       |  |  |  |

|               | погми оизими оинных современной                                                  | электроники вы зниете!                                                                       |  |  |  |

|              | электронной компонентной базы,                                                       | – Каких производителей ПЛИС вы                                        |

|--------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|              | справочными материалами;                                                             | знаете?                                                               |

|              |                                                                                      | – Основной мировой производитель                                      |

|              |                                                                                      | процессорных ІР ядер?                                                 |

|              |                                                                                      | – Что такое OpenCores?                                                |

|              |                                                                                      | – Назовите крупнейших представите-                                    |

|              |                                                                                      | лей кремниевых фабрик?                                                |

|              |                                                                                      | – Каких производителей САПР элек-                                     |

|              |                                                                                      | троники вы знаете?                                                    |

|              |                                                                                      | – Каких зарубежных и отечественных                                    |

|              |                                                                                      | производителей вакуумной электрони-                                   |

|              |                                                                                      | ки вы знаете?                                                         |

| ПК-5 готовно | <br>сть выполнять расчет и проектиров                                                | ание электронных приборов, схем и                                     |

|              |                                                                                      | ия в соответствии с техническим за-                                   |

|              | льзованием средств автоматизации п                                                   |                                                                       |

|              | <u> </u>                                                                             |                                                                       |

| знать        | – основные этапы проектирования электронных приборов, схем и                         | – Что такое язык описания аппара-<br>туры HDL.                        |

|              | устройств. Концепцию сквозного                                                       | туры ПDL.<br>– Каковы преимущества разработки                         |

|              | проектирования;                                                                      | схемы на базе HDL по сравнению со                                     |

|              | <ul><li>– элементную базу современной</li></ul>                                      | схемон на оазе 1191 по сравнению со схемотехническим способом.        |

|              | электроники. Основные САПР сквоз-                                                    | <ul><li>- Что такое логический синтез схе-</li></ul>                  |

|              | ного проектирования электронных                                                      |                                                                       |

|              | приборов, схем и устройств;                                                          | Mbl.                                                                  |

|              | <ul><li>приооров, ехем и устроиств,</li><li>основные методы проектирования</li></ul> | – Какие САПР разработки ИС вы зна-<br>eme?                            |

|              | электронных систем (схемотехни-                                                      |                                                                       |

|              | ческое проектирование, на основе                                                     | – Какие САПР для разработки схем на базе ПЛИС вы знаете?              |

|              | HDL, системное проектирование);                                                      | – Логический синтез ИС на стан-                                       |

|              | , T                                                                                  | дартных ячейках.                                                      |

|              |                                                                                      | <ul><li>Логический синтез схем на ПЛИС.</li></ul>                     |

|              |                                                                                      | – Что такое критический путь циф-                                     |

|              |                                                                                      | ровой схемы?                                                          |

|              |                                                                                      | – Какие языки описания аппаратуры                                     |

|              |                                                                                      | вы знаете?                                                            |

|              |                                                                                      | <ul><li>Чем отличаются синтезируемые</li></ul>                        |

|              |                                                                                      | структуры языка HDL от несинтези-                                     |

|              |                                                                                      | руемых?                                                               |

|              |                                                                                      | - Какими способами можно повысить                                     |

|              |                                                                                      | - Какими способами можно повысить  быстродействие цифровой схемы?     |

|              |                                                                                      | - В чём заключается компромисс пло-                                   |

|              |                                                                                      | – в чем заключается компромисс пло-<br>щадь кристалла/быстродействие? |

|              |                                                                                      |                                                                       |

|              |                                                                                      | <ul><li>- Что такое синхронная цифровая<br/>схема?</li></ul>          |

|              |                                                                                      | скопи:                                                                |

| уметь        | – анализировать техническое зада-                                                    | – Разработать одноразрядную схему                                     |

|              | ние, пользоваться проектной доку-                                                    | сравнения на вентильном уровне на                                     |

|              | ментацией;                                                                           | языке VHDL.                                                           |

|              | – осуществлять выбор элементной                                                      | – Разработать на языке VHDL схему                                     |

|              | базы при проектировании электрон-                                                    | дешифратора 2 в 4.                                                    |

ных приборов, схем и устройств в соответствии с техническим заданием. Осуществлять выбор необходимых САПР;

проектировать электронные приборы схемы и устройства на основе различных методов проектирования (схемотехническое, на основе HDL, системное проектирование) с использованием САПР;

- Разработать на языке VHDL схему преобразователя двоичного кода в семисегментный.

- Разработать модуль на VHDL, вычисляющий четырехвходовую функцию XOR (исключающее ИЛИ).

- Разработать на языке VHDL схему 4-х разрядного счётчика.

- Разработать на языке VHDL схему 4-х разрядного сумматора чисел со знаком.

- Разработать на языке VHDL схему 8-и разрядного регистра.

- Разработать на языке VHDL схему сдвигового регистра с параллельной загрузкой.

- Разработать на языке VHDL схему конечного автомата для детектирования переднего фронта сигнала.

#### владеть

- навыками работы с проектной документацией, информационными базами данных об отечественных и зарубежных компонентах;

- навыками работы с основными

САПР электронных приборов, схем и устройств;

- основными методами проектирования (схемотехническое, на основе HDL, системное проектирование);

- Реализовать одноразрядную схему сравнения на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- Реализовать схему дешифратора 2 в 4 на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- Реализовать схему преобразователя двоичного кода в семисегментный на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- Реализовать четырехвходовую функцию XOR (исключающее ИЛИ) на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- Реализовать схему 4-х разрядного счётчика на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- Реализовать схему 4-х разрядного сумматора чисел со знаком на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

- Реализовать схему 8-и разрядного регистра на базе ПЛИС Spartan 3E.

Определить быстродействие схемы и затраченные ресурсы ПЛИС.

— Реализовать схему сдвигового реги-

стра с параллельной загрузкой на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

– Реализовать схему детектирования переднего фронта сигнала на базе ПЛИС Spartan 3E. Определить быстродействие схемы и затраченные ресурсы ПЛИС.

ПК-6 способность разрабатывать проектную и техническую документацию, оформлять законченные проектно-конструкторские работы

знать

- Основные формы представления проектной документации в соответствии с требованиями ЕСКД;

- Стандартные опции САПР для формирования проектной документации;

- Правила организации многоуровневой проектной документации для сложных проектов;

- Перечислите основные этапы производства ИС

- Что включает в себя спецификация на разрабатываемую ИС

- Какова иерархия проектирования СБИС.

- Что такое кремниевый уровень проектирования. Какие примитивы применяются на данном уровне.

- Что такое транзисторный уровень проектирования. Какие примитивы применяются на данном уровне.

- Что такое вентильный уровень проектирования. Какие примитивы применяются на данном уровне.

- Что такое регистровый уровень проектирования. Какие примитивы применяются на данном уровне.

- Что такое процессорный уровень проектирования. Какие примитивы применяются на данном уровне.

- Что такое системный уровень проектирования. Какие примитивы применяются на данном уровне.

- В чём заключается принцип управления сложностью (абстрагирование) при разработке электроники.

- Какова современная инфраструктура производства ИС.

- Что такое ІР-блок.

- Классификация IP-блоков

- Что представляют собой топологические IP-блоки.

- Этапы проектирования заказной

| уметь   | - анализировать техническое задание на проект, пользоваться проектной документацией; - использовать стандартные опции САПР для формирования проектной документации; - разрабатывать многоуровневую проектную документацию для сложных проектов с помощью САПР; | ИС.  — Этапы проектирования ИС на стандартных ячейках.  — Этапы проектирования схемы на базе ПЛИС.  — Разработать двухразрядную схему сравнения на основе двух экземпляров одноразрядной схемы сравнения. Использовать комментарии для описания кода.  — Разработать на языке VHDL схему дешифратора 3 в 8 на основе экземпляров схемы дешифратора 2 в 4. Использовать комментарии для описания кода.  — Разработать на языке VHDL схему 16-и разрядного сумматора чисел со знаком на основе экземпляров 4-х разрядного сумматора чисел со знаком на основе экземпляров 4-х разрядного сумматора. Использовать комментарии для описания кода.  — Разработать на языке VHDL схему 8-и разрядного регистра. Использовать комментарии для описания кода.  — Разработать на языке VHDL схему конечного автомата для реализации |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| владеть | <ul> <li>навыками работы с проектной документацией;</li> <li>стандартными опциями САПР для формирования проектной документации;</li> <li>навыками работы с различными САПР для осуществления документооборота между ними;</li> </ul>                           | защиты от дребезга. Использовать комментарии для описания кода.  Подготовить проектную документацию: RTL-код и файл ограничений (топологических и временных) для реализации проекта на базе ПЛИС для следующих проектов:  Восьмиразрядная схема сдвига с управляющим входом, определяющим направление сдвига.  Приоритетный шифратор 8 в 3  Преобразователь двоичного кода в двоично-десятичный  4-х разрядный сумматор чисел с плавающей точкой.  8-и разрядный ГІГО буфер  4-х разрядный ШИМ  Сторожевой таймер  Схема стека  Арифметико-логическое устройство  Регистровый файл                                                                                                                                                                                                                                         |

|  | – Схема деления |

|--|-----------------|

|  |                 |

б) Порядок проведения промежуточной аттестации, показатели и критерии оценивания:

Промежуточная аттестация по дисциплине «Основы проектирования электронной компонентной базы» включает теоретические вопросы, позволяющие оценить уровень усвоения обучающимися знаний, и практические задания, выявляющие степень сформированности умений и владений, проводится в форме зачёта.

#### Показатели и критерии оценивания зачёта:

- на оценку «зачтено» обучающийся демонстрирует высокий или средний уровень сформированности компетенций: основные знания, умения освоены, но допускаются незначительные ошибки, неточности, затруднения при аналитических операциях, переносе знаний и умений на новые, нестандартные ситуации.

- на оценку «не зачтено» обучающийся демонстрирует знания не более 20% теоретического материала, допускает существенные ошибки, не может показать интеллектуальные навыки решения простых задач.

# 8 Учебно-методическое и информационное обеспечение дисциплины (модуля)

#### а) Основная литература:

- 1. Мурсаев, А. Х. Практикум по проектированию на языках VerilogHDL и SystemVerilog: учебное пособие / А. Х. Мурсаев, О. И. Буренева. 2-е изд., стер. Санкт-Петербург: Лань, 2018. 120 с. ISBN 978-5-8114-2560-0. Текст: электронный // Лань : электронно-библиотечная система. URL: <a href="https://e.lanbook.com/book/103142">https://e.lanbook.com/book/103142</a> (дата обращения: 20.10.2020). Режим доступа: для авториз. пользователей.

- 2. Петров, М. Н. Моделирование компонентов и элементов интегральных схем: учебное пособие / М. Н. Петров, Г. В. Гудков. Санкт-Петербург: Лань, 2011. 464 с. ISBN 978-5-8114-1075-0. Текст: электронный // Лань: электронно-библиотечная система. URL: <a href="https://e.lanbook.com/book/661">https://e.lanbook.com/book/661</a> (дата обращения: 20.10.2020). Режим доступа: для авториз. пользователей.

#### Дополнительная литература:

1. Щука, А. А. Электроника: Учебное пособие / Щука А.А. - СПб:БХВ-Петербург, 2008. - 751 с.ISBN 978-5-9775-0160-6. - Текст : электронный. - URL: <a href="https://znanium.com/catalog/product/350420">https://znanium.com/catalog/product/350420</a> (дата обращения: 21.10.2020). — Режим доступа: по подписке.

#### Методические указания:

Методические рекомендации по выполнению практических заданий представлены в приложении 1.

#### Программное обеспечение и интернет ресурсы:

- 1. ISE WebPACK Xilinx [Программное обеспечение].

- 2. VHDL for FPGA Design Wikibooks, open books for an open world [Электронный ресурс].—https://en.wikibooks.org/wiki/VHDL\_for\_FPGA\_Design.

3. Digital Circuits - Wikibooks, open books for an open world [Электронный ресурс]. – Режим доступа: <a href="https://en.wikibooks.org/wiki/Digital Circuits">https://en.wikibooks.org/wiki/Digital Circuits</a>.

# 9 Материально-техническое обеспечение дисциплины (модуля)

Материально-техническое обеспечение дисциплины включает:

| Тип и название аудитории       | Оснащение аудитории                           |

|--------------------------------|-----------------------------------------------|

| Лекционная аудитория           | Мультимедийные средства хранения, передачи и  |

|                                | представления информации                      |

| Компьютерный класс             | Персональные компьютеры с установленным спе-  |

|                                | циализированном ПО для проектирования эле-    |

|                                | ментной базы (ISE WebPACK Xilinx).            |

| Аудитория для самостоятельной  | Персональные компьютеры с установленным спе-  |

| работы: компьютерный класс     | циализированном ПО для проектирования эле-    |

|                                | ментной базы (ISE WebPACK Xilinx).            |

| Аудитории для групповых и ин-  | Аудитории кафедры электроники и микроэлектро- |

| дивидуальных консультаций, те- | ники (ауд. 457,458,459,460).                  |

| кущего контроля и промежуточ-  |                                               |

| ной аттестации                 |                                               |

| Помещение для хранения и       | Стеллажи, сейфы для хранения учебного         |

| профилактического обслуживания | оборудования. Инструменты для ремонта         |

| учебного оборудования          | оборудования.                                 |

# Министерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования «Магнитогорский государственный технический университет им. Г.И. Носова»

(ФГБОУ ВО «МГТУ им. Г.И. Носова»)

# Методические указания основы проектирования электронной компонентной базы

Разработал: к.т.н., доцент каф. ЭиМЭ Швидченко Н.В.

Магнитогорск, 2017

#### Введение

Традиционное схемное проектирование достигло в своем развитии предела и используется в настоящее время лишь для сравнительно простых проектов разрабатываемой электроники. Основным недостатком схемного описания проектов сложной электроники, включающей большое количество компонентов и модулей, является высокая трудоемкость отладки. На смену схемному описанию пришли языки описания аппаратуры, такие как VHLD и Verilog. В отличие от традиционных языков программирования, описывающих последовательность выполняемых команд, языки описания аппаратуры описывают структуру и связи разрабатываемого устройства. Такое описание разрабатываемого устройства называется структурным (параллельным). Второй подход к описанию устройства называется поведенческим (последовательным). При таком подходе описывается не структура устройства, а порядок его функционирования (поведение). Языки описания аппаратуры включат как параллельные, так и последовательные функции, т.е. с их помощью можно описать как структуру разрабатываемого устройства, так и его поведение в зависимости от входных воздействий. Здесь следует сделать важное замечание:

Последовательное (поведенческое) описание устройства не всегда может быть корректно скомпилировано в синтезируемые конструкции, т.е. синтезированная схема устройства может работать не так, как задумывал разработчик. В тоже время структурное (параллельное) описание однозначно синтезируется в описанную структуру. Таким образом, при описании разрабатываемого устройства следует отдавать предпочтение структурному описанию или, как говорят, использовать синтезируемые конструкции. Последовательное (поведенческое) описание в свою очередь эффективно используется на этапе функционального моделирования работы разрабатываемого устройства. Тем не менее, использование последовательных операторов языков описания аппаратуры для синтеза разрабатываемого устройства допускается при условии жесткого соблюдения ряда правил (данные правила будут рассмотрены в соответствующей лабораторной работе).

Данные методичесские призван научить основам проектирования электроники с помощью языка описания аппаратуры VHLD. При этом основной упор делается на развитие навыков написания грамотного и самое главное синтезируемого кода, т.е. такого кода, который будет гарантированно скомпилирован в работающую схему. Поэтому вместо подробного описания синтаксиса VHLD и всевозможных конструкций языка практикум ограничивается обзором сравнительно небольшого набора синтезируемых конструкций, использующих десяток типовых шаблонов VHDL-кода, синтезируемых в типовые схемы. Данные шаблоны могут быть легко интегрированы при проектировании больших сложных систем.

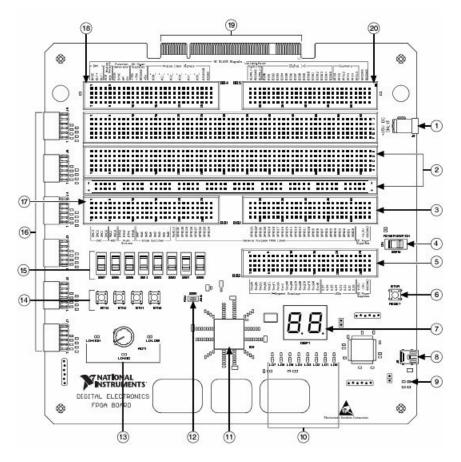

Для обеспечения процесса сквозного проектирования вплоть до готового устройства было решено использовать программируемую логику (ПЛИС), а именно отладочную плату NI Digital Electronics FPGA Board на основе ПЛИС Xilinx Spartan-3E. В качестве программного обеспечения используется САПР ICE WebPACK фирмы Xilinx.

#### Описание платы NI Digital Electronics FPGA

Плата **NI Digital Electronics FPGA** является результатом совместного сотрудничества компаний NI и Xilinx, являющихся крупнейшими в мире производителями программного обеспечения измерительных систем и программируемых логических интегральных схем (ПЛИС). Внешний вид платы NI Digital Electronics FPGA представлен на рисунке 1. NI Digital Electronics FPGA Board содержит шесть каналов для ввода аналоговых входных сигналов AIO — AI5, а также 32 цифровые входные (выходные) линии общего пользования — GPIO31.

Описание сигналов, подаваемых на сигнальные зоны макетирования: ВВ1 — зона макетирования для подключения к ЦАП, АЦП, кнопкам, движковым переключателям, внешнему синхросигналу и линиям общего назначения ПЛИС. ВВ2 - зона макетирования для подключения к линиям общего назначения ПЛИС и источникам питания. ВВ3 - зона макетирования для управления семисегментным индикатором на два знакоместа, светодиодами, подключения к источникам питания ВВ4 - зона макетирования для подключения к сигналам NI ELVIS, включая аналоговые входные сигналы, функциональные генераторы, источники питания, цифровые входные/выходные сигналы. ВВ5 — зона макетирования для подключения к сигналам NI ELVIS, включая регулируемые источники питания, цифровые входные/выходные сигналы, выходные сигналы счётчиков, общие точки сигналов.

Рисунок 1 – Внешний вид платы NI Digital Electronics FPGA Board:

1— разъем питания (15B); 2—макетной платы для возможности создания дополнительной обвязки; 3— блок макетной платы BB2; 4— выключатель питания; 5— блок макетной платы BB3; 6— кнопка сброса; 7— семисегментные индикаторы; 8— USB-соединитель; 9— LD-G- светодиод; 10— светодиоды; 11— FPGA Xilinx Spartan 3E; 12— переключатель прошивки ПЛИС через ROM/JTAG; 13— датчик угла поворота с кнопкой; 14— кнопки; 15— движковые переключатели; 16— 6 коннекторов типа PMOD (2x6); 17— блок макетной платы BB1; 18— блок макетной платы BB4; 19— (NI ELVIS)- соединитель; 20— блок макетной платы BB5; 21— программатор; 22— кварцевый генератор 50МГц; 23— защита платы от статического электричества

### Краткое описание CAПР WebPack

**WebPACK** — это САПР проектирования цифровых устройств на базе микросхем ПЛИС CPLD и FPGA фирмы Xilinx. Данная система является бесплатным вариантом коммерческой САПР этой же фирмы под названием ISE и доступна для свободного скачивания через сеть Internet (www.xilinx.com). Основное отличие бесплатной версии от ее платного аналога состоит в отсутствии поддержки микросхем, емкость которых выше 1,5 млн системных вентилей.

WebPACK состоит из набора модулей, каждый из которых выполняет свои специализированные функции. Основные модули пакета следующие:

- редактор схемного ввода;

- текстовый редактор с поддержкой языков описания аппаратуры VHDL и Verilog;

- CORE Generator генератор оптимизированных IP-ядер;

- редактор тестовых воздействий для программы моделирования;

- программа функционального и временного моделирования;

- генератор VHDL/Verilog кода;

- программа автоматического размещения и трассировки ПЛИС;—программы «ручного» размещения и оптимизации проекта;

- программа загрузки конфигурационной последовательности в ПЛИС FPGA и программирования ПЛИС CPLD и ППЗУ.

Большинство модулей САПР WebPACK имеют как графический интерфейс пользователя, так и интерфейс командной строки. САПР WebPACK может работать под операционными системами Windows, Linux и Sun Solaris.

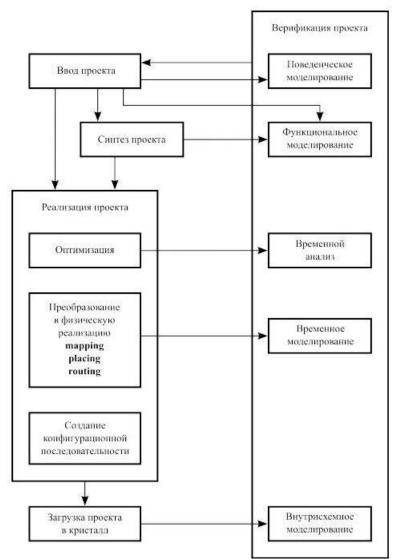

Процесс разработки цифровых устройств в среде WebPACK состоит из следующих этапов.

- 1. Ввод описания проектируемого устройства в схемотехнической форме или с использованием языков описания аппаратуры (HDL), таких, как VHDL и Verilog.

- 2. Синтез устройства, то есть преобразование описания устройства, полученного на первом этапе, в описание на уровне логических вентилей.

- 3. Реализация устройства, то есть преобразование описания устройства на уровне логических вентилей в физическое описание для конкретной микросхемы ПЛИС.

- 4. Формирование конфигурационной последовательности для микросхемы ПЛИС.

После каждого из этапов 1,2 и 3 возможно, а в большинстве случаев и необходимо для успешного завершения проекта выполнение процедуры моделирования и верификации полученного описания устройства.

На рисунке 2 представлена обобщенная схема проектирования цифровых устройств в CAПР WebPACK.

Рисунок 2 - Обобщенная схема проектирования цифровых устройств в САПР WebPACK

#### Проектирование комбинационных схем на вентильном уровне

#### Введение

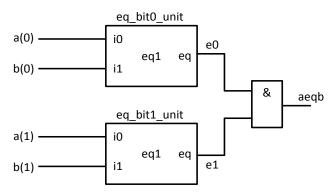

В данной главе на примере простой схемы сравнения подробно рассмотрена структура синтезируемого VHDL-кода. Описание работы цифровых комбинационных схем в данной работе представлено исключительно на вентильном уровне абстракции (gate level), т.е. применяются только базовые логические вентили, реализующие основные логические операции (НЕ, И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ). Рассмотрен структурный (иерархический) подход к проектированию цифровых систем, при котором система на верхнем уровне проектирования рассматривается как соединение более простых унифицированных блоков, которые, в свою очередь, также строятся из более простых блоков и т.д.

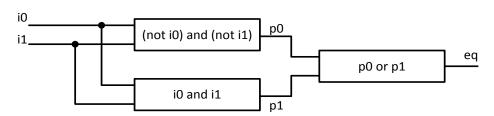

#### 1.1 Описание схем в дизъюнктивной нормальной форме

Рассмотрим одноразрядную схему сравнения (1-bit equality comparator) , содержащую два входа i0, i1 и один выход eq. Выход eq схемы сравнения принимает активное значение при условии, что входы i0 и i1 эквивалентны. Таблица истинности (truth table) одноразрядной схемы сравнения представлена в таблице 1.1.

Таблица 1.1 – Таблица истинности одноразрядной схемы сравнения

| i0 | i1 | eq |

|----|----|----|

| 0  | 0  | 1  |

| 0  | 1  | 0  |

| 1  | 0  | 0  |

| 1  | 1  | 1  |

Допустим, что для реализации одноразрядной схемы сравнения мы решили использовать базовые логические вентили (logic gates), такие как: *HE* (*NOT*), *U* (*AND*), *ИЛИ* (*OR*), *Исключающее ИЛИ* (*XOR*). Одной из форм записи логической функции, описывающей работу схемы, является запись функции в совершенной дизъюнктивной нормальной форме, т.е. в виде суммы минтермов (sum-of-products canonical form) . Логическая функция одноразрядной схемы сравнения, записанная в совершенной дизъюнктивной нормальной форме, имеет вид:

$$eq = i0 \cdot i1 + \overline{i0} \cdot \overline{i1}$$

Один из возможных вариантов VHDL-кода, описывающего рассматриваемую схему сравнения приведен в листинге 1.1. Проанализируем языковые конструкции приведенного кода в следующих подразделах.

Листинг 1 - Реализация одноразрядной схемы сравнения на вентильном уровне

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity eq1 is

Port ( i0 : in STD_LOGIC;

i1 : in STD_LOGIC;

eq : out STD_LOGIC);

end eq1;

architecture sop_arch of eq1 is

signal p0 , p1 : STD_LOGIC;

begin

```

#### 1.1.1 Основные лексические правила

Код VHDL является нечувствительным к способу написания (регистру) символов (case insensitive), т.е. прописные и строчные буквы являются взаимозаменяемыми. Кроме того в коде VHDL допускается вставлять дополнительные пробелы и пустые строки. Использование дополнительных пробелов и пустых строк позволяет сделать код более понятным.

**Идентификатором** в языке VHDL называется имя объекта (константы, переменной, функции, сигнала, порта, подпрограммы, объекта проекта, метки). Идентификатор может содержать до 26 букв, цифр и нижних подчеркиваний (не допускается использовать более одного символа нижнего подчеркивания подряд). Начинаться идентификатор должен только с буквы. В примере (листинг 1.1) используются следующие идентификаторы: eq1, i0, i1, eq, sop\_arch, p0, p1.

В языке VHDL существуют зарезервированные ключевые слова. В данном учебном пособии все ключевые слова выделены синим цветом (листинг 1.1).

Комментарий начинается с двух смежных дефисов и продолжается до конца строки. При синтезе VHDL-проекта комментарии игнорируются. В данном учебном пособии все комментарии выделены зеленым цветом (листинг 1.1).

#### 1.1.2 Используемые библиотеки

Описание объекта на VHDL состоит из трех частей (листинг 1.1): объявления используемых библиотек (library, use), описания интерфейса объекта (entity) и его внутренней структуры (architecture).

Первые две строчки в примере (листинг 1.1) объявляют используемые библиотеки:

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

```

В данном случае объявляется библиотека IEEE.STD\_LOGIC\_1164, что позволяет использовать соответствующие типы данных, операторы и функции, определенные в данной библиотеке.

#### 1.1.3 Интерфейс объекта

Описание интерфейса (entity declaration) включает в себя объявление имени объекта и объявление входных и выходных портов объекта. Ниже приведено описание интерфейса из примера (листинг 1.1):

```

entity eq1 is -- декларация имени объекта

Port ( i0 , i1 : in STD_LOGIC; -- декларация входных портов

eq : out STD_LOGIC); -- декларация выходного порта

end eq1;

```

В данном примере в первой строке объявляется имя объекта eq1. Структура port описывает входные и выходные порты в следующем формате:

```

имя_порта1, имя_порта2, . . . : режим_сигнала тип_сигнала;

```

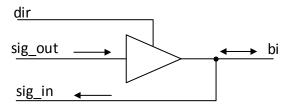

Для входных портов указывается входной режим сигнала (in), для выходных портов указывается выходной режим сигнала (out). Также предусмотрен режим inout для двунаправленных портов.

#### 1.1.4 Тип данных и операторы

VHDL — язык со строгой типизацией. Это значит, что данные определенного типа могут принимать значения, соответствующие только данному типу (например, логический тип данных BOOLEAN может принимать только значения ИСТИНА (TRUE) и ЛОЖНО (FALSE) и никакие другие) и с данными определенного типа могут выполняться операции, соответствующие только данному типу (например, для данных типа BOOLEAN используются только логические операторы). Несмотря на то, что в языке VHDL применяется множество типов данных, в данном учебном пособии используются далеко не все — в основном применяется тип STD\_LOGIC и его варианты. Это связано с тем, что основной упор в данном учебном пособии сделан на синтезируемые конструкции языка VHDL, т.е. такие конструкции, на основе которых может быть синтезирована реально работающая схема.