# Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования «Магнитогорский государственный технический университет им. Г.И. Носова» Многопрофильный колледж

# МЕТОДИЧЕСКИЕ УКАЗАНИЯ ДЛЯ ЛАБОРАТОРНЫХ И ПРАКТИЧЕСКИХ ЗАНЯТИЙ МЕЖДИСЦИПЛИНАРНОГО КУРСА

МДК.01.01 Цифровая схемотехника

для обучающихся специальности

09.02.01 Компьютерные системы и комплексы

# ОДОБРЕНО

Предметно-цикловой комиссией «Информатика и вычислительная техника» Председатель \_\_\_\_\_/Т.Б. Ремез Протокол № 6 от «25»января 2023 г.

Методической комиссией МпК Протокол № 4 от «8» февраля 2023 г.

# Разработчик:

преподаватель ФГБОУ ВО «МГТУ им. Г.И. Носова» Многопрофильный колледж Татьяна Борисовна Ремез

Методические указания по выполнению практических и лабораторных работ разработаны на основе рабочей программы профессионального модуля 01 «Проектирование цифровых систем» МДК.01.01 «Цифровая схемотехника».

Содержание практических и лабораторных работ ориентировано на подготовку обучающихся к освоению вида деятельности ВД 1 «Проектирование цифровых систем» программы подготовки специалистов среднего звена по специальности 09.02.01. Компьютерные системы и комплексы и овладению профессиональными компетенциями.

# СОДЕРЖАНИЕ

| 1 ВВЕДЕНИЕ              | 4  |

|-------------------------|----|

| 2 МЕТОДИЧЕСКИЕ УКАЗАНИЯ | 5  |

| Практическое занятие 1  | 5  |

| Практическое занятие 2  | 6  |

| Практическое занятие 3  | 11 |

| Практическое занятие 4  | 12 |

| Практическое занятие 5  | 14 |

| Практическое занятие 6  | 15 |

| Практическое занятие 7  | 16 |

| Практическое занятие 8  | 18 |

| Практическое занятие 9  | 20 |

| Практическое занятие 10 | 22 |

| Практическое занятие 11 | 24 |

| Практическое занятие 12 | 26 |

| Практическое занятие 13 | 34 |

| Лабораторное занятие 1  | 40 |

| Лабораторное занятие 2  | 44 |

| Лабораторное занятие 3  | 47 |

| Лабораторное занятие 4  | 50 |

| Лабораторное занятие 5  | 55 |

| Лабораторное занятие 6  | 59 |

| Лабораторное занятие 7  | 62 |

| Лабораторное занятие 8  | 67 |

| Лабораторное занятие 9  | 70 |

| Лабораторное занятие 10 | 73 |

#### 1 ВВЕДЕНИЕ

Важную часть теоретической и профессиональной практической подготовки студентов составляют практические и лабораторные занятия.

Состав и содержание практических и лабораторных работ направлены на реализацию действующего федерального государственного образовательного стандарта среднего профессионального образования.

Ведущей дидактической целью практических занятий является формирование практических умений - профессиональных (умений выполнять определенные действия, операции, необходимые в последующем в профессиональной деятельности), необходимых в последующей учебной деятельности по профессиональным модулям.

Ведущей дидактической целью лабораторных работ является экспериментальное подтверждение и проверка существенных теоретических положений (законов, зависимостей). В соответствии с рабочей программой ПМ.01. «Проектирование цифровых систем», МДК.01.01 «Цифровая схемотехника» предусмотрено проведение практических и лабораторных занятий.

В результате их выполнения, обучающийся должен:

## уметь:

- выполнять анализ и синтез схем цифровых устройств;

- проводить исследования работы цифровых устройств и проверку их на работоспособность;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции;

Содержание практических и лабораторных занятий ориентировано на подготовку обучающихся к освоению профессионального модуля программы подготовки специалистов среднего звена по специальности и овладению *профессиональными компетенциями*:

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

- ПК 1.4. Выполнять прототипирование цифровых систем, в том числе с применением виртуальных средств.

#### А также формированию общих компетенций:

- OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 02. Использовать современные средства поиска, анализа и интерпретации информации, и информационные технологии для выполнения задач профессиональной деятельности;

- ОК 04 Эффективно взаимодействовать и работать в коллективе и команде.

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 06 Проявлять гражданско-патриотическую позицию, демонстрировать осознанное поведение на основе традиционных российских духовно-нравственных ценностей, в том числе с учетом гармонизации межнациональных и межрегилиозных отношений, применять стандарты антикоррупционного поведения;

- ОК 07 Содействовать сохранению окружающей среды, ресурсосбережению, применять знания об изменении климата, принципы бережливого производства, эффективно действовать в чрезвычайных ситуациях;

- OК 08 Использовать средства физической культуры для сохранения и укрепления здоровья в процессе профессиональной деятельности и поддержания необходимого уровня физической подготовленности;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

Выполнение обучающимися практических и лабораторных работ по ПМ.01 «Проектирование цифровых систем», МДК.01.01 «Цифровая схемотехника» направлено на:

- обобщение, систематизацию, углубление, закрепление, развитие и детализацию полученных теоретических знаний по конкретным темам междисциплинарных курсов;

- формирование умений применять полученные знания на практике, реализацию единства интеллектуальной и практической деятельности;

- формирование и развитие умений: наблюдать, сравнивать, сопоставлять, анализировать, делать выводы и обобщения, самостоятельно вести исследования, пользоваться различными приемами измерений, оформлять результаты в виде таблиц, схем, графиков;

- приобретение навыков работы с различными приборами, аппаратурой, установками и другими техническими средствами для проведения опытов;

- развитие интеллектуальных умений у будущих специалистов: аналитических, проектировочных, конструктивных и др.;

- выработку при решении поставленных задач профессионально значимых качеств, таких как самостоятельность, ответственность, точность, творческая инициатива.

Практические и лабораторные занятия проводится после соответствующей темы, которая обеспечивает наличие знаний, необходимых для ее выполнения.

# 2 МЕТОДИЧЕСКИЕ УКАЗАНИЯ

# **Тема 1.1. Арифметические и логические основы цифровой** техники

# Практическое занятие № 1 Системы счисления

**Цель:** закрепить знания об основных системах счисления, используемых в цифровой технике.

#### Выполнив работу, Вы будете:

уметь.

- выполнять анализ и синтез схем цифровых устройств.

#### Выполнение практической работы способствует формированию:

- ОК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

**Материальное обеспечение:** для проведения практической работы наличие специальных материалов и оборудования не требуется.

Задание 1. Данные для выполнения задания приведены в таблице 1 (по вариантам).

- 1) определите количество разрядов числа;

- 2) запишите алфавит данной системы счисления;

- 3) запишите число в виде полинома. В общем виде

$$x = a_n \times p^n + a_{n-1} \times p^{n-1} + a_{n-2} \times p^{n-2} + \dots + a_1 \times p^1 + a_0 \times p^0$$

Таблица 1 – Исходные данные

| Вариант | Число                  | Вариант | Число                 | Вариант | Число                  |

|---------|------------------------|---------|-----------------------|---------|------------------------|

| 1       | 2564852 <sub>10</sub>  | 11      | 2612264 <sub>8</sub>  | 21      | 54896213 <sub>10</sub> |

| 2       | $362570_{8}$           | 12      | B14B4 <sub>16</sub>   | 22      | 321323125 <sub>8</sub> |

| 3       | $1101011_2$            | 13      | 4589723 <sub>10</sub> | 23      | 345A655 <sub>16</sub>  |

| 4       | $3B9C781E_{16}$        | 14      | 21404233 <sub>8</sub> | 24      | $1100101_2$            |

| 5       | 25978631 <sub>10</sub> | 15      | $46089B_{16}$         | 25      | 789562 <sub>10</sub>   |

| 6       | 1110011 <sub>2</sub>   | 16      | 1001101 <sub>2</sub>  | 26      | 232150 <sub>8</sub>    |

| 7       | 1456987 <sub>10</sub>  | 17      | 3658921 <sub>10</sub> | 27      | 13468 <sub>16</sub>    |

| 8       | 5435533 <sub>8</sub>   | 18      | 15752251 <sub>8</sub> | 28      | $110110_2$             |

| 9       | $163B5B_{16}$          | 19      | 37D4A9 <sub>16</sub>  | 29      | 4523698 <sub>10</sub>  |

| 10      | 726196 <sub>10</sub>   | 20      | 110011 <sub>2</sub>   | 30      | $4506B2_{16}$          |

**Задание 2.** Переведите число из двоичной системы счисления в десятичную систему счисления. Полученное десятичное число переведите в восьмеричную и шестнадцатеричную систему счисления. Данные для выполнения задания приведены в таблице 2 (по вариантам).

Таблица 2 - Исходные данные

| Вариант | Число     | Вариант | Число      | Вариант | Число     |

|---------|-----------|---------|------------|---------|-----------|

| 1       | 1101100   | 11      | 1011010000 | 21      | 111001010 |

| 2       | 111100000 | 12      | 1100100001 | 22      | 110000010 |

| 3       | 110001011 | 13      | 1110010000 | 23      | 11100110  |

| 4  | 1000001001 | 14 | 110000001  | 24 | 110100100  |

|----|------------|----|------------|----|------------|

| 5  | 1001011000 | 15 | 110010100  | 25 | 1011110010 |

| 6  | 1110011    | 16 | 1000001101 | 26 | 100100010  |

| 7  | 100100111  | 17 | 11011010   | 27 | 1000101011 |

| 8  | 101000001  | 18 | 101101110  | 28 | 11000011   |

| 9  | 1010001110 | 19 | 10001010   | 29 | 110000110  |

| 10 | 111000000  | 20 | 11001000   | 30 | 101000011  |

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

# Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если ход выполнения задания верный, но была допущена одна или две ошибки, приведшие к неправильному ответу.

Оценка «удовлетворительно» ставится, если в работе не получен ответ и приведено неполное выполнение задания, но ход выполнения задания верный

Оценка «неудовлетворительно» ставится, если задание не выполнено или если приведен правильный ответ, но решение отсутствует.

# Практическое занятие № 2 Анализ и синтез цифровых логических схем

**Цель:** закрепить знания об основных логических функциях, научиться строить логические схемы по логическим выражениям, выполнять анализ и синтез схем цифровых устройств;.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

# Выполнение практической работы способствует формированию:

- OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

**Материальное обеспечение:** для проведения практической работы наличие специальных материалов и оборудования не требуется.

#### Краткие теоретические сведения

*Анализ комбинационной схемы* — это составление полного описания, которое содержит таблицу истинности, логические функции, временные диаграммы.

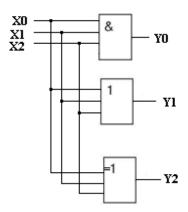

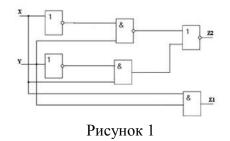

**Пример 1.** Выполнить анализ комбинационной схемы (рис. 1): составить логическую функцию, таблицу истинности, временные диаграммы.

#### Решение:

Заданная схема имеет три входных сигнала X0, X1, X2 и три выходных сигнала У0, У1, У2. Запишем для каждого выходного сигнала логическую функцию:

$$Y0 = X0 \cdot X1 \cdot X2$$

$$Y1 = X0 \lor X1 \lor X2$$

$$Y2 = X0 \oplus X1 \oplus X2$$

Рисунок SEQ Рисунок \\* ARABIC 1 - Комбинационная схема

Таблица истинности (табл. 3) содержит значения выходных сигналов (аргументов), соответствующие различным комбинациям входных сигналов. Схема имеет три входа (X0, X1, X2), для которых существует  $2^3$ =8 вариантов набора. Таблица составлена в соответствии с логикой работы элементов.

Таблица 3 - Таблица истинности

| № |    | Аргументы |    | Функции |    |    |  |

|---|----|-----------|----|---------|----|----|--|

|   | X0 | X1        | X2 | У0      | У1 | У2 |  |

| 0 | 0  | 0         | 0  | 0       | 0  | 0  |  |

| 1 | 0  | 0         | 1  | 0       | 1  | 1  |  |

| 2 | 0  | 1         | 0  | 0       | 1  | 1  |  |

| 3 | 0  | 1         | 1  | 0       | 1  | 0  |  |

| 4 | 1  | 0         | 0  | 0       | 1  | 1  |  |

| 5 | 1  | 0         | 1  | 0       | 1  | 0  |  |

| 6 | 1  | 1         | 0  | 0       | 1  | 0  |  |

| 7 | 1  | 1         | 1  | 1       | 1  | 1  |  |

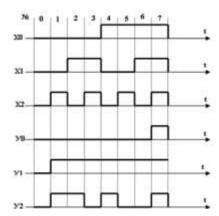

Рисунок 2 - Временные диаграммы, поясняющие работу схемы

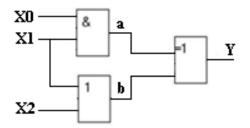

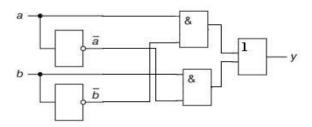

**Пример 2.** Выполнить анализ комбинационной схемы (рис.3): составить логическую функцию, таблицу истинности, временные диаграммы.

Рисунок 3 – Комбинационная схема

#### Решение:

Дополнительно обозначим внутренние узлы схемы a и b и добавим для этих узлов столбцы в таблице истинности (табл. 4). Сигнал a формируется логическим элементом И, на входы которого поданы сигналы X0 и X1. Сигнал b формируется элементом ИЛИ, на входы которого поступают сигналы X1 и X2. Сигналы a и b позволяют определить выходной сигнал Y по правилам логического элемента «Искл. ИЛИ». Временные диаграммы приведены на рисунке 4.

Таблица 4 - Таблица истинности

| No |    | Аргументы |    |   | Функции |   |  |  |

|----|----|-----------|----|---|---------|---|--|--|

|    | X0 | X1        | X2 | a | b       | Y |  |  |

| 0  | 0  | 0         | 0  | 0 | 0       | 0 |  |  |

| 1  | 0  | 0         | 1  | 0 | 1       | 1 |  |  |

| 2  | 0  | 1         | 0  | 0 | 1       | 1 |  |  |

| 3  | 0  | 1         | 1  | 0 | 1       | 1 |  |  |

| 4  | 1  | 0         | 0  | 0 | 0       | 0 |  |  |

| 5  | 1  | 0         | 1  | 0 | 1       | 1 |  |  |

| 6  | 1  | 1         | 0  | 1 | 1       | 0 |  |  |

| 7  | 1  | 1         | 1  | 1 | 1       | 0 |  |  |

Рисунок 4 - Временные диаграммы

Составление логической функции по заданной схеме. Сначала записываем уравнения для вспомогательных сигналов a и b, а затем для выходного сигнала Y.

$$a = X0 \cdot X1$$

$$b = X1 \lor X2$$

$$Y = a \oplus b = (X0 \cdot X1) \oplus (X1 \lor X2)$$

$\it Cuhmes комбинационных \it cxem -$  это проектирование и разработка устройства по определенным правилам.

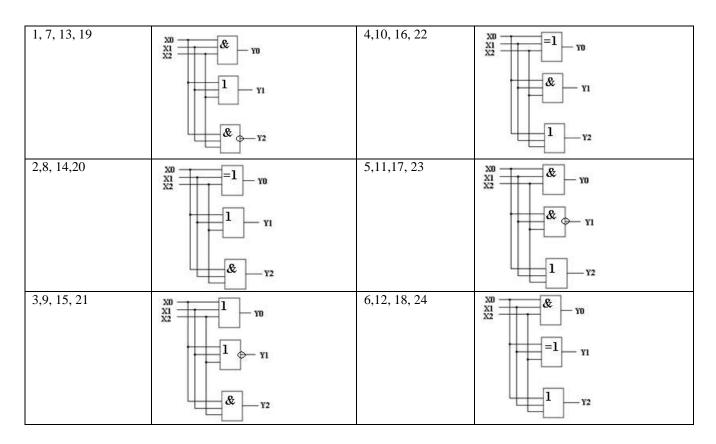

**Пример 3.** Выполнить синтез комбинационной схемы, заданной логической функцией; составить таблицу истинности, временную диаграмму. Логическая функция

$$Y = (a \cdot \underline{b}) \vee (b \cdot \underline{a})$$

Решение:

Для построения логической схемы, реализующей логическую функцию, необходимо логические элементы, предназначенные для выполнения логических операций располагать, начиная от входа в порядке, указанном в выражении (рис.5).

Рисунок 5 – Логическая схема

Логическое уравнение содержит два аргумента a и b и их инверсии  $\underline{a}$ ,  $\underline{b}$ . На входы логических элементов И подаются a,  $\underline{b}$  и  $\underline{a}$ , b соответственно. Результаты логического умножения подаются на вход логического сложения (функция ИЛИ).

Таблица истинности содержит четыре комбинации входных аргументов (табл. 5). Временные диаграммы приведены на рисунке 6.

Таблица 5 - Таблица истинности

| а | b | <u>a_</u> | <u>b</u> | a · <u>b</u> | b ⋅ <u>a</u> | Y |

|---|---|-----------|----------|--------------|--------------|---|

| 0 | 0 | 1         | 1        | 0            | 0            | 0 |

| 0 | 1 | 1         | 0        | 0            | 1            | 1 |

| 1 | 0 | 0         | 1        | 1            | 0            | 1 |

| 1 | 1 | 0         | 0        | 0            | 0            | 0 |

**Пример 4.** Построить структуру логического устройства, реализующего логическую функцию  $y = (a + b + c)(a + b + c)(\underline{a} + b + c)(\underline{a} + \underline{b} + c)$

Рисунок 6 - Временные диаграммы

Рисунок 7 – Схема логического устройства

Структура логического устройства, реализующего логическую функцию, приведена на рисунке 7.

#### Практические задания

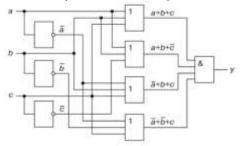

**Задание 1.** Выполнить анализ комбинационной схемы: составить логическую функцию, таблицу истинности, временные диаграммы. Данные для выполнения задания приведены в таблице 6 (по вариантам).

Таблица 6 – Исходные данные для выполнения задания 1

|  | Вариант |  | Baj | риант |  |  |

|--|---------|--|-----|-------|--|--|

|--|---------|--|-----|-------|--|--|

**Задание 2.** Выполнить анализ комбинационной схемы: составить логическую функцию, таблицу истинности, временные диаграммы. Данные для выполнения задания приведены в таблице 7 (по вариантам).

Таблица 7 – Исходные данные для выполнения задания 2

| Тиолици     | пеходиве даниве для выполнения | 300 <u>,</u>  |                        |

|-------------|--------------------------------|---------------|------------------------|

| Вариант     |                                | Вариант       |                        |

| 1,7, 13, 19 | ХО Т<br>Х1 Т & Y<br>Х2 Т       | 2,10,16,22    | X0                     |

| 3,8,14, 20  | X0                             | 4,11, 17, 23  | X0 1                   |

| 5,9,15, 21  | X0<br>X1<br>1<br>Y<br>X2       | 6, 12, 18, 24 | X0 =1<br>X1 =1<br>X2 1 |

**Задание 3.** Выполнить синтез комбинационной схемы, заданной логической функцией. Данные для выполнения задания приведены в таблице 8 (по вариантам). Таблица 8 – Исходные данные для выполнения задания 3

| Вариант               | Логическая функция                                                                          |

|-----------------------|---------------------------------------------------------------------------------------------|

| 1, 6, 11, 16, 21, 26  | $y = (\overline{a}b + \overline{c})(\overline{a} + \overline{b} + c)(a + b + c)$            |

| 2, 7, 12, 17, 22, 27  | $y = (a + b + \overline{c})(\overline{a} + \overline{b}c)(a + \overline{b} + \overline{c})$ |

| 3, 8, 13, 18, 23, 28  | $y = (b + a\overline{c})(\overline{a} + bc)(a + \overline{b} + c)$                          |

| 4, 9, 14, 19, 24, 29  | $y = (\overline{a}\overline{b}+\overline{c})(a+\overline{b}+c)(ab+\overline{c})$            |

| 5, 10, 15, 20, 25, 30 | $y = (a + \overline{b}c)(\overline{a} + b + \overline{c})(ab + c)$                          |

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

# Форма представления результата:

Отчет по работе должен содержать:

- 4) наименование работы и цель работы;

- 5) результаты работы;

- 6) выводы по работе.

# Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если ход выполнения задания верный, но была допущена одна или две ошибки, приведшие к неправильному результату.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

Тема 1.2. Интегральное исполнение базовых цифровых элементов

# Практическое занятие № 3 Определение параметров и характеристик интегральных микросхем (ИМС) логических элементов

**Цель:** закрепить знания о параметрах и характеристиках ИМС, об условно-графических обозначениях, маркировке, типах корпусов ИМС.

#### Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств.

#### Выполнение практической работы способствует формированию:

- OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

**Задание:** определите параметры и характеристики интегральных микросхем (ИМС) логических элементов. Исходные данные для выполнения заданий приведены в таблице 9 (по вариантам). Для выполнения заданий используйте справочники, интернет-ресурсы или другие информационные источники.

Таблица 9 - Исходные данные

| ва<br>ри | M HMG               | ва<br>ри | N IDIG                | ва<br>ри | W ING               | ва<br>ри | W IIVG                |

|----------|---------------------|----------|-----------------------|----------|---------------------|----------|-----------------------|

| т        | Маркировка ИМС      | ан<br>т  | Маркировка ИМС        | ан<br>т  | Маркировка ИМС      | ан<br>т  | Маркировка ИМС        |

| 1        | К176ЛИ1<br>К155ЛЕ3  | 8        | 564ЛС1<br>КР1531ЛИ1   | 15       | К176ЛИ1<br>К155ЛЛ1  | 22       | 564ЛС1<br>КР1531ЛА3   |

| 2        | К176ЛС1<br>533ЛА1   | 9        | 564 ЛП13<br>133ЛА1    | 16       | К176ЛС1<br>533ЛА2   | 23       | 564 ЛП13<br>133ЛЕ1    |

| 3        | К176ЛП12<br>К555ЛИ6 | 10       | К176ЛИ1<br>К555ЛИ6    | 17       | К176ЛП12<br>К555ЛИ4 | 24       | К176ЛИ1<br>К555ЛИ4    |

| 4        | 564ЛС1<br>К155ЛЛ1   | 11       | К176ЛС1<br>533ЛА1     | 18       | 564ЛС1<br>133ЛЛ1    | 25       | К176ЛС1<br>533ЛА7     |

| 5        | 564 ЛП13<br>1531ЛА3 | 12       | К176ЛП12<br>КР1531ЛИ1 | 19       | 564 ЛП13<br>1531ЛА1 | 26       | К176ЛП12<br>КР1531ЛП5 |

| 6        | К176ЛИ1<br>133ЛЕ1   | 13       | 564ЛС1<br>533ЛА1      | 20       | К176ЛИ1<br>133ЛЕ2   | 27       | 564ЛС1<br>КР531ЛА19   |

| 7        | К176ЛС1<br>133ЛА1   | 14       | 564 ЛП13<br>133ЛЕ1    | 21       | К176ЛС1<br>133ЛА2   | 28       | 564 ЛП13<br>К555ЛП12  |

# Порядок выполнения работы:

- 1) определите функциональное назначение микросхемы;

- 2) зарисуйте условно-графическое обозначение микросхемы с основными выводами;

- 3) определите условное обозначение корпуса по ГОСТ;

- 4) зарисуйте корпус и запишите его характеристики.

- 5) определите параметры микросхем и заполните таблицу 10.

Таблица 10 – Параметры микросхем логических элементов

| Маркировка<br>ИМС | Тип<br>логики | Напряжение<br>питания, В | Потребляемая мощность, мВт | Время<br>задержки,<br>нс | Коэффициент<br>разветвления | Максимальная частота входного сигнала, МГц |

|-------------------|---------------|--------------------------|----------------------------|--------------------------|-----------------------------|--------------------------------------------|

| 1                 |               |                          |                            |                          |                             |                                            |

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

#### Практическое занятие №4

# Определение параметров и характеристик ИМС транзисторно-транзисторной логики (ТТЛ), логики комплементарный металл-оксид-полупроводник (КМОП)

**Цель:** закрепить знания о параметрах и характеристиках ИМС ТТЛ и КМОП, об условнографических обозначениях, маркировке, типах корпусов ИМС ТТЛ и КМОП.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

#### Выполнение практической работы способствует формированию:

- ОК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

Задание: определите параметры и характеристики интегральных микросхем (ИМС). Исходные данные для выполнения заданий приведены в таблице 10 (по вариантам). Для выполнения заданий используйте справочники, интернет-ресурсы или другие информационные источники.

Таблица 10 - Исходные данные

| Вариант | Маркировка<br>ИМС | Вариант | Маркировка<br>ИМС | Вариант | Маркировка<br>ИМС | Вариант | Маркировка<br>ИМС |

|---------|-------------------|---------|-------------------|---------|-------------------|---------|-------------------|

| 1       | K155PE23          | 8       | К155ИЕ5           | 15      | КР531ИД7          | 22      | 155ИД4            |

|         | 564ИМ1            |         | 564ИД1            |         | К176ПУ5           |         | К176ИЕ4           |

| 2       | 134ИД6            | 9       | 530PT1            | 16      | К555ИД5           | 23      | К555ИД5           |

|         | К176ИР4           |         | 564TP2            |         | 564ИП3            |         | К176ЛС1           |

| 3       | КР531РУ8          | 10      | KP531TB9          | 17      | K155PE23          | 24      | КР531РУ8          |

|         | 564TM3            |         | К176ЛС1           |         | 564ИД4            |         | 564ЛП13           |

| 4       | 533ИД6            | 11      | 133ТЛ1            | 18      | 155ИД4            | 25      | 533ИД6            |

|         | К176ИЕ4           |         | 564TM3            |         | 564ИД5            |         | К176РУ2А          |

| 5       | К155РУ7           | 12      | 155TM8            | 19      | К155РУ            | 26      | К155РУ7           |

|         | К176ЛС1           |         | 564ЛП13           |         | 564ИМ1            |         | 564ИД1            |

| 6       | 133ИМ3            | 13      | 530PT1            | 20      | K155PE23          | 27      | 133ИМ3            |

|         | К176РУ2А          |         | 564ИЕ11           |         | К176ИР4           |         | 564TP2            |

| 7       | 530PT1            | 14      | 533ИД6            | 21      | 134ИД6            | 28      | 530PT1            |

|         | 564ЛП13           |         | К176ЛИ1           |         | 564TM3            |         | 564ЛП13           |

#### Порядок выполнения работы:

#### Для каждой ИМС:

- 1) определите функциональное назначение микросхемы;

- 2) зарисуйте условно-графическое обозначение микросхемы с основными выводами;

- 3) определите условное обозначение корпуса по ГОСТ;

- 4) зарисуйте корпус и запишите его характеристики.

- 5) определите параметры микросхем и заполните таблицу 11.

Таблица 11 - Параметры микросхем

| Маркировка | Тип    | Напряжение | Потребляемая  | Время     | Коэффициент  | Максимальная     |

|------------|--------|------------|---------------|-----------|--------------|------------------|

| ИМС        | логики | питания, В | мощность, мВт | задержки, | разветвления | частота входного |

| PHVIC      |        |            |               | нс        |              | сигнала, МГц     |

| 1          |        |            |               |           |              |                  |

| 2          |        |            |               |           |              |                  |

6) Запишите выражение, соответствующее приведенной логической схеме:

7) Запишите логическое выражение из таблицы истинности (по вариантам):

|   | Входы |   |           |           | Выход      | ды (№ вар  | ианта)     |            | ,          |

|---|-------|---|-----------|-----------|------------|------------|------------|------------|------------|

|   |       |   | 1,8,15,22 | 2,9,16,23 | 3,10,17,24 | 4,11,18,25 | 5,12,19,26 | 6,13,20,27 | 7,14,21,28 |

| A | В     | C | F         | F         | F          | F          | F          | F          | F          |

| 0 | 0     | 0 | 1         | 0         | 0          | 1          | 1          | 0          | 1          |

| 0 | 0     | 1 | 0         | 1         | 0          | 0          | 1          | 1          | 1          |

| 0 | 1     | 0 | 0         | 0         | 1          | 0          | 0          | 1          | 0          |

| 0 | 1     | 1 | 1         | 1         | 1          | 1          | 0          | 0          | 1          |

| 1 | 0     | 0 | 1         | 0         | 0          | 0          | 1          | 1          | 0          |

| 1 | 0     | 1 | 0         | 0         | 1          | 1          | 0          | 0          | 0          |

| 1 | 1     | 0 | 1         | 1         | 0          | 0          | 1          | 1          | 0          |

| 1 | 1     | 1 | 0         | 1         | 1          | 0          | 0          | 0          | 1          |

<sup>8)</sup> Полученное в п.7 логическое выражение реализовать на реальных ИМС логических элементов серий К155, 555: построить 2 варианта схемы и сравнить их между собой по показателям.

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

# Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

Тема 1. 3. Цифровые последовательностные устройства (ЦПУ): триггеры

# Практическое занятие №5 Определение параметров и характеристик ИМС триггеров

**Цель:** закрепить знания о параметрах и характеристиках ИМС триггеров, научиться выполнять синтез триггеров.

#### Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств.

# Выполнение практической работы способствует формированию:

OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

Задание 1. Исходные данные по вариантам приведены в таблице 12.

- 1) запишите назначение интегральной микросхемы, зарисуйте УГО;

- 2) определите тип корпуса по ГОСТ и зарисуйте корпус ИМС;

- 3) укажите в таблице 13 параметры и характеристики микросхемы триггера.

Таблица 12 - Исходные данные

| Вариант | Маркировка | Вариант | Маркировка | Вариант | Маркировка | Вариант | Маркировка |

|---------|------------|---------|------------|---------|------------|---------|------------|

|         | ИМС        |         | ИМС        |         | ИМС        |         | ИМС        |

| 1       | K155TB1    | 7       | K555TM7    | 13      | 564TM3     | 19      | K176TM1    |

| 2       | 564TM3     | 8       | 564TM2     | 14      | 533TP2     | 20      | 133TB1     |

| 3       | 133TB1     | 9       | 533TM7     | 15      | 564TB1     | 21      | 564TM2     |

| 4       | 564TP2     | 10      | 564TB1     | 16      | 134TB13    | 22      | K555TP2    |

| 5       | K155TM7    | 11      | K155TM5    | 17      | 564TP2     | 23      | 564TM3     |

| 6       | K176TM1    | 12      | K555TP2    | 18      | K155TB1    | 24      | 134TB13    |

Таблица 13 - Параметры микросхем триггеров

| Маркировка | Тип    | Потребляемая  | Напряжение | Время                 | Коэффициент      | Максимальная |

|------------|--------|---------------|------------|-----------------------|------------------|--------------|

| ИМС        | логики | мощность, мВт | питания, В | задержки,             | разветвления,    | частота      |

|            |        |               |            | t <sub>зад</sub> , нс | K <sub>pa3</sub> | входного     |

|            |        |               |            |                       | •                | сигнала, МГц |

|            |        |               |            |                       |                  |              |

## Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

# Практическое занятие №6 Синтез триггеров различных типов

Цель: научиться выполнять синтез триггеров.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

# Выполнение практической работы способствует формированию:

- OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

## Краткие теоретические сведения

Принципы работы и особенности синтеза триггеров показаны в примерах 1 и 2.

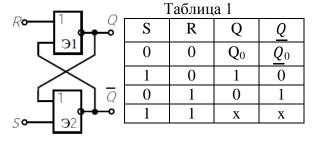

**Пример 1.** Составить таблицу состояний для *RS*-триггера на элементах ИЛИ–НЕ, схема которого приведена на рис. 1.

<u>Решение:</u> При S = R = 0 состояние элементов зависит от сигналов на выходах Q и  $\underline{Q}$ . Пусть Q = 0. Тогда логический элемент Э2 имеет на входах 00 и на выходе  $\underline{Q} = 1$ . Логический элемент Э1 имеет на входах 01 и на выходе Q = 0, т.е. схема сохраняет предыдущее состояние. При S = 1, R = 0 на выходе элемента Э2 всегда Q = 0. На входе Э1 оба сигнала 00, на выходе сигнал Q = 1.

Сигналы S = 0, R = 1 устанавливают элемент 91 при любом предшествующем состоянии в состояние Q=0, а 92- в состояние Q=1. Если R=S=1, то Q=Q=0, что недопустимо для триггера. Эти сигналы запрещены (табл. 1, где x- неопределенное состояние).

Рис.1

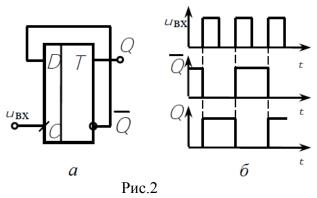

**Пример 2.** Составить схему Т-триггера на основе D-триггера, срабатывающего по переднему фронту синхроимпульса. Начертить временную диаграмму его работы.

<u>Решение:</u> приходом синхроимпульса D-триггер устанавливается в состояние Q = D. Поэтому соединяем его вход D с выходом  $\underline{Q}$ . Схема приведена на рис. 2a, а временные диаграммы – на рисунке 2б.

Практические задания:

- 1. Составить таблицу состояний для RS-триггера на элементах И–НЕ. Начертить условное графическое обозначение такого триггера.

- 2. Какой сигнал установится на выходах Q и  $\underline{Q}$  JK-триггера, если к приходу синхроимпульса: а) J = 1, K = 0; б) K = 1, J = 0; в) K = 1, J = 1?

- 3. Составить схему Т-триггера на основе ЈК-триггера, привести временные диаграммы его работы (с опорой на конспект темы 1.3).

- 4. Для микросхемы триггера (по вариантам, таблица 14):

- 1) запишите тип триггера;

- 2) изобразите условно-графическое обозначение микросхемы триггера и его корпуса;

- 3) запишите уравнение функционирования триггера данного типа;

- 4) составьте таблицу истинности триггера;

- 5) нарисуйте временную диаграмму триггера.

Таблица 14 - Исходные данные

| Вариант | Маркировка | Вариант | Маркировка | Вариант | Маркировка | Вариант | Маркировка |

|---------|------------|---------|------------|---------|------------|---------|------------|

|         | ИМС        |         | ИМС        |         | ИМС        |         | ИМС        |

| 1       | K155TB1    | 7       | K555TM7    | 13      | 564TM3     | 19      | K176TM1    |

| 2       | 564TM3     | 8       | 564TM2     | 14      | 533TP2     | 20      | 133TB1     |

| 3       | 133TB1     | 9       | 533TM7     | 15      | 564TB1     | 21      | 564TM2     |

| 4       | 564TP2     | 10      | 564TB1     | 16      | 134TB13    | 22      | K555TP2    |

| 5       | K155TM7    | 11      | K155TM5    | 17      | 564TP2     | 23      | 564TM3     |

| 6       | K176TM1    | 12      | K555TP2    | 18      | K155TB1    | 24      | 134TB13    |

# Форма представления результата:

Отчет по работе должен содержать:

- 1. наименование работы и цель работы;

- 2. необходимые теоретические сведения (примеры выполнения заданий);

- 3. выполненные задания (схемы и временные диаграммы обязательно);

- 4. выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

Тема 1.4. Цифровые последовательностные устройства (ЦПУ): счётчики

# Практическое занятие №7 Синтез счётных схем

Цель: научиться выполнять синтез счётных схем.

## Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

# Выполнение практической работы способствует формированию:

- ОК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

# Краткие теоретические сведения

Принципы работы и особенности синтеза и анализа счетчиков представлены в примере.

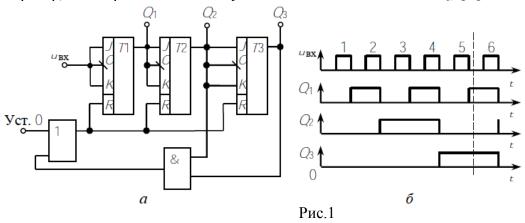

**Пример.** Составить схему последовательного суммирующего счетчика импульсов с модулем счета K = 6 на JK-триггерах. Начертить временные диаграммы его работы.

<u>Решение.</u> Последовательный счетчик должен содержать N триггеров, так чтобы число возможных состояний схемы  $2^N$  было равно или больше модуля счета K. При N = 3  $2^3$ =8> K=6. Два состояния схемы избыточны. Схема должна переходить в исходное состояние  $Q_3Q_2Q_1$ =000 после шестого импульса, когда  $Q_3Q_2Q_1$ =110. Это достигается с помощью логической схемы, подающей при таком наборе выходных сигналов сигнал на входы R. Схема счетчика приведена на рис. 1, а, а временные диаграммы – на рис. 1, б.

Например, после прихода пятого импульса в счетчике записано число  $Q_3Q_2Q_1=101_2=5_{10}$

#### Практические задания

1. Используя структурную схему счетчика, заполните таблицу:

| Обозначение       | Назначение вывода счетчика. |

|-------------------|-----------------------------|

| вывода счетчика   |                             |

| $S_0S_n$          |                             |

| $S_0S_n$ $Q_0Q_n$ |                             |

| M                 |                             |

| V                 |                             |

| P                 |                             |

| С                 |                             |

| R                 |                             |

| Up                |                             |

| Dn                |                             |

- 2. Составить схему последовательного суммирующего счетчика на ЈК-триггерах с модулем счета К = 7. Какая комбинация будет на выходе счетчика после: а) 6 импульсов, б) 12 импульсов?

- 3. Составить схему последовательного суммирующего счетчика импульсов на D-триггерах с модулем счета K = 4. Начертить временные диаграммы его работы.

- 4. Составить схему последовательного суммирующего счетчика импульсов на RST-триггерах с модулем счета K = 3. Начертить временные диаграммы его работы. Каково состояние выходов счетчика после прихода 5 импульсов (укажите на диаграмме)?

- 5. Согласно своему варианту (Таблица 15), выполните следующие задания:

- 1) определите функциональное назначение микросхемы;

- 2) зарисуйте условно-графическое обозначение микросхемы с основными выводами;

- 3) определите условное обозначение корпуса по ГОСТ;

- 4) зарисуйте корпус и запишите его параметры

- 5. определите параметры микросхем и заполните таблицу

Таблица 15 - Исходные данные

| Вариант | Маркировка | Вариант | Маркировка | Вариант | Маркировка | Вариант | Маркировка |

|---------|------------|---------|------------|---------|------------|---------|------------|

|         | ИМС        |         | ИМС        |         | ИМС        |         | ИМС        |

| 1       | К155ИЕ5    | 7       | К555ИЕ15   | 13      | К176ИЕ12   | 19      | К176ИЕ18   |

| 2       | 564ИЕ14    | 8       | 564ИЕ14    | 14      | 533ИЕ10    | 20      | КМ555ИЕ10  |

| 3       | 133ИЕ5     | 9       | 533ИЕ15    | 15      | К176ИЕ13   | 21      | К176ИЕ1    |

| 4       | 564ИЕ11    | 10      | 564ИЕ11    | 16      | 134ИЕ5     | 22      | К555ИЕ18   |

| 5       | К155ИЕ9    | 11      | К155ИЕ10   | 17      | К176ИЕ17   | 23      | К176ИЕ5    |

| 6       | К176ИЕ1    | 12      | К555ИЕ19   | 18      | К155ИЕ9    | 24      | 533ИЕ19    |

Таблица 2 - Параметры микросхем триггеров

| Маркировка | Тип    | Потребляемая  | Напряжение | Время                 | Коэффициент   | Максимальная |

|------------|--------|---------------|------------|-----------------------|---------------|--------------|

| ИМС        | логики | мощность, мВт | питания, В | задержки,             | разветвления, | частота      |

|            |        |               |            | t <sub>зад</sub> , нс | $K_{pa3}$     | входного     |

|            |        |               |            |                       | •             | сигнала, МГц |

|            |        |               |            |                       |               |              |

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

# Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

# Тема 1.6. Цифровые комбинационные устройства (ЦКУ): мультиплексоры и демультиплексоры Практическое занятие №8 Анализ и синтез схем мультиплексоров

Цель: научиться выполнять анализ и синтез схем мультиплексоров.

#### Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

#### Выполнение практической работы способствует формированию:

- ОК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

# Краткие теоретические сведения

Принципы работы и особенности синтеза и анализа мультиплексоров и демультиплексоров рассмотрены в примерах.

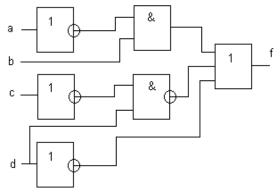

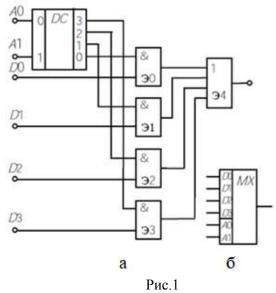

**Пример 1.** Составить схему мультиплексора для передачи сигналов от четырех источников по одной линии.

<u>Решение</u>. Схема должна содержать 4 входа и 1 выход. Кроме того, она должна включать блок управления выборки источника (адрес). Этот блок удобно выполнить в виде дешифратора. В двоичном коде номер любого из четырех источников можно задать двухразрядным числом, которое выбирается на входах A1, A0. В качестве ключей используются элементы И, каждый из которых управляется сигналом с выхода дешифратора. Выходы ключей объединяются элементом ИЛИ, на выход которого подключается линия связи. Схема мультиплексора приведены на рис. 1, а, а его условное обозначение на рис. 1 б.

Пусть на входы A0, A1 подан сигнал 01 (адрес источника D1). Высокий уровень с выхода дешифратора поступает на вход Э1, и сигнал на его выходе повторяет сигнал источника D1. Через Э4 он поступает в линию связи. Все остальные элементы закрыты.

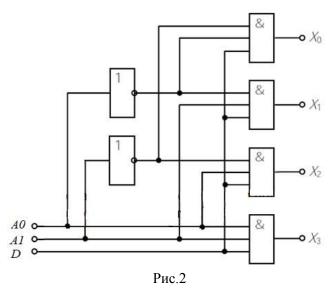

**Пример 2.** Составить схему демультиплексора для управляемой передачи информации, поступающей по одному D входу на четыре выхода:  $X_0$ ,  $X_1$ ,  $X_2$ ,  $X_3$ . Отметим, что демультиплексор реализует операцию противоположную той, которую осуществляет мультиплексор.

<u>Решение.</u> В общем случае число выходных линий N определяется количеством адресных входов n и равно  $N=2^n$ . Так как по условию число выходов N=4, то необходимое число адресных входов n=2: A0, A1. Функционирование демультиплексора осуществляется в соответствии с табл. 1. Из нее следует, что информация D, поступающая на вход в соответствии с кодом адреса, передается на одну из выходных линий  $X_i$ . При этом на остальные линии информация не поступает и на них поддерживается уровень логического «0».

Логические функции демультиплексора по таблице истинности 1 имеют вид:

Таблица 1.

$$X_0 = \overline{A0} \cdot \overline{A1} \cdot D;$$

$$X_1 = \overline{A0} \cdot A1 \cdot D;$$

$$X_2 = A0 \cdot \overline{A1} \cdot D;$$

$$X_3 = A0 \cdot A1 \cdot D.$$

Схема демультиплексора представлена на рис. 2. Она включает два инвертора и четыре элемента И:

#### Практические задания

- 1. Составить схему мультиплексора для передачи информации от трех источников по одной линии.

- 2. Используя схемы мультиплексора и демультиплексора, составить схему передачи информации от трех источников трем приемникам по одной линии связи.

- 3. Составить схему мультиплексора  $2 \to 1$  для передачи информации от двух источников (D0, D1) на выход F в соответствии с кодом адреса (0 или 1). Логическая функция, описывающая работу мультиплексора:

$$Y = (X0 \cdot A) + (X1 \cdot A)$$

Начертить условное графическое обозначение мультиплексора.

- 4. Составить схему демультиплексора для управляемой передачи информации, поступающей по одному D входу на два выхода: X<sub>0</sub>, X<sub>1</sub>.

- 5. Постройте схему мультиплексора по уравнению:

$$Y = \underline{\left(\underline{X0} \cdot \underline{X1} \cdot \underline{X2}\right) + \left(\underline{X0} \cdot X1 \cdot X2\right) + \left(X0 \cdot \underline{X1} \cdot X2\right) + \left(X0 \cdot X1 \cdot \underline{X2}\right)}$$

- 6. Для интегральной микросхемы К155КП8:

- а) определите функциональное назначение;

- б) зарисуйте условно-графическое обозначение;

- в) составьте таблицу истинности.

## Форма представления результата:

Отчет по работе должен содержать:

- 1. наименование работы и цель работы;

- 2. необходимые теоретические сведения (примеры выполнения заданий);

- 3. выполненные задания (схемы и временные диаграммы обязательно);

- 4. выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если все задания выполнены верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение заданий.

Оценка «неудовлетворительно» ставится, если задания не выполнены.

Тема 1.7. Цифровые комбинационные устройства (ЦКУ): преобразователи кодов, шифраторы и дешифраторы

# Практическое занятие №9

Определение характеристик ИМС преобразователей кодов, шифраторов и дешифраторов

**Цель:** закрепить знания о параметрах и характеристиках ИМС преобразователей кодов, (де)шифраторов.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств.

# Выполнение практической работы способствует формированию:

- ОК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

**Практическое задание:** определите параметры и характеристики интегральных микросхем. Исходные данные приведены в таблице 16 (по вариантам). Заполните таблицу 17.

Таблица 16 – Исходные данные

|                | , , ,          | r <u>`</u>     |                |                |                | 1              |                |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| ва<br>ри<br>ан | Маркировка ИМС |

| T              |                | T              |                | T              |                | T              |                |

| 1              | 133ИД3         | 8              | 133ИД4         | 15             | 133ИД4         | 22             | КР531ИД7       |

|                | 530ИД7         |                | КР531ИД14      |                | КР531ИД7       |                | 155ИД4         |

|                | К555ИД5        |                | К555ИД5        |                | К555ИД5        |                | К555ИД5        |

| 2              | КР531ИД7       | 9              | 533ИД3         | 16             | 133ИД4         | 23             | 133ИД3         |

|                | 155ИД4         |                | 133ИД4         |                | КР531ИД14      |                | 530ИД14        |

|                | К555ИД5        |                | К555ИД4        |                | К555ИД5        |                | К555ИД4        |

| 3              | 133ИД3         | 10             | КР531ИД7       | 17             | 533ИД3         | 24             | КР531ИД14      |

|                | 530ИД14        |                | 155ИД4         |                | 133ИД4         |                | 155ИД4         |

|                | К555ИД4        |                | К555ИД5        |                | К555ИД4        |                | К555ИД5        |

| 4              | КР531ИД14      | 11             | 533ИД5         | 18             | 133ИД3         | 25             | 133ИД4         |

|                | 155ИД4         |                | 133ИД4         |                | 530ИД14        |                | КР531ИД14      |

|                | К555ИД5        |                | К555ИД5        |                | К555ИД4        |                | К555ИД5        |

| 5              | 155ИД3         | 12             | 133ИД4         | 19             | КР531ИД14      | 26             | 533ИД3         |

|                | КР531ИД14      |                | КР531ИД14      |                | 155ИД4         |                | 133ИД4         |

|                | К555ИД4        |                | К555ИД5        |                | К555ИД5        |                | К555ИД4        |

| 6              | 133ИД4         | 13             | 533ИД3         | 20             | 155ИД3         | 27             | 133ИД4         |

|                | КР531ИД7       |                | 133ИД4         |                | КР531ИД14      |                | КР531ИД7       |

|                | К555ИД5        |                | К555ИД4        |                | К555ИД4        |                | К555ИД5        |

| 7              | 133ИД3         | 14             | 133ИД4         | 21             | 133ИД4         | 28             | КР531ИД14      |

|                | 530ИД14        |                | КР531ИД14      |                | КР531ИД14      |                | 155ИД4         |

|                | К555ИД4        |                | К555ИД5        |                | К555ИД5        |                | К555ИД5        |

Таблица 17 – Параметры микросхем

| ИМС | Тип<br>логики | Потребляемая мощность, мВт | Напряжение<br>питания, В | Время<br>задержки,<br>t <sub>зад</sub> , нс | Коэффициент разветвления, $K_{pas}$ | Максимальная частота входного сигнала, МГц | Назначение |

|-----|---------------|----------------------------|--------------------------|---------------------------------------------|-------------------------------------|--------------------------------------------|------------|

|     |               |                            |                          |                                             |                                     |                                            |            |

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

#### 3) выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если задание выполнено верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение задания.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

# Практическое занятие №10

#### Изучение схемы управления семисегментным индикатором

**Цель:** закрепить знания о параметрах и характеристиках ИМС преобразователей кодов, (де)шифраторов.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

# Выполнение практической работы способствует формированию:

- OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

#### Краткие теоретические сведения

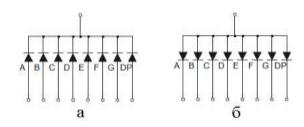

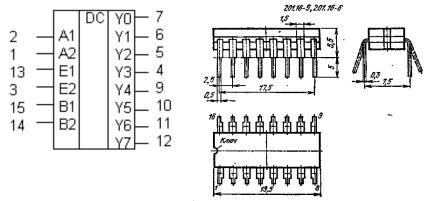

Семисегментные светодиодные индикаторы предназначены для отображения арабских цифр от 0 до 9.

Такие индикаторы бывают одноразрядные, которые отображают только одно число, но семисегментных групп, объединенных в один корпус, может быть и больше (многоразрядные). В этом случае цифры разделяются децимальной точкой.

Индикатор называется семисегментным из-за того, что отображаемый символ строится из отдельных семи сегментов. Внутри корпуса такого индикатора находятся светодиоды, каждый из которых засвечивает свой сегмент.

Буквы и другие символы на таких индикаторах отображать проблематично, поэтому для этих целей используются 16-сегментные индикаторы.

Светодиодные индикаторы бывают двух типов. В первом из них все катоды, т.е. отрицательные выводы всех светодиодов, объединены вместе и для них выделен соответствующий вывод на корпусе. Остальные выводы индикатора соединены к аноду каждого из светодиодов (рис.9, а). Такая схема называется «схема с общим катодом». Также существуют индикаторы, у которых светодиоды каждого из сегментов подключены по схеме с общим анодом (рис.9, б).

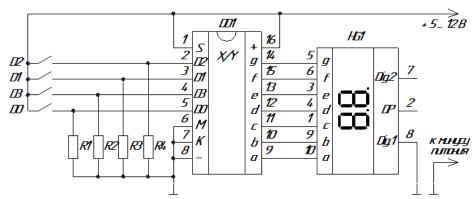

Для управления семисегментным индикатором часто используется дешифратор К176ИД2.

Эта микросхема способна преобразовать двоичный код, состоящий из нулей и единиц в десятичные цифры от 0 до 9.

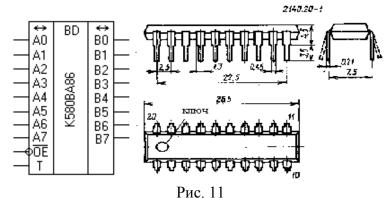

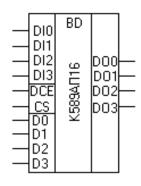

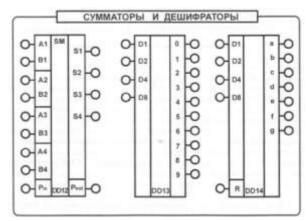

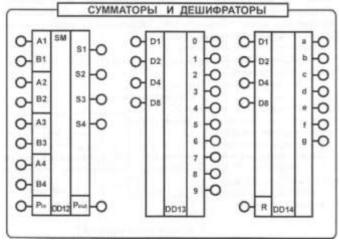

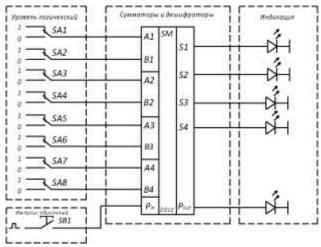

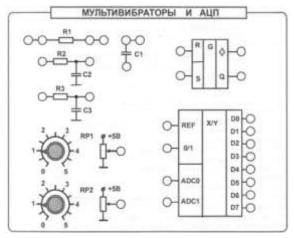

Схема управления представлена на рисунке 10. Дешифратор К176ИД2 выполнен в корпусе DIP16. Он имеет семь выходных вывода (выводы 9 - 15), каждый из которых предназначен для определенного сегмента. Управление точкой здесь не предусмотрено. Также микросхема имеет четыре входа (выводы 2 - 5) для подачи двоичного кода. На 16-й и 8-ой вывод подается плюс и минус питания соответственно. Остальные три вывода являются вспомогательными.

В схеме присутствует четыре тумблера (кнопки), при нажатии на них на входы дешифратора подается логическая единица от плюса питания. Также в схеме присутствует четыре резистора. Они нужны, чтобы гарантировать на логическом входе низкий уровень, при отсутствии сигнала. Без них показания на индикаторе могут отображаться некорректно. Рекомендуется использовать одинаковые сопротивления от 10 кОм до 100 кОм.

На схеме выводы 2 и 7 индикатора HG1 (GND-5622As-21) не подключены. Если подключить к минусу питания вывод DP, то будет светиться децимальная точка. А если подать минус на вывод Dig.2, то будет светиться и вторая группа сегментов (будет показывать тот же символ).

Рисунок 10 – Схема управления семисегментным индикатором

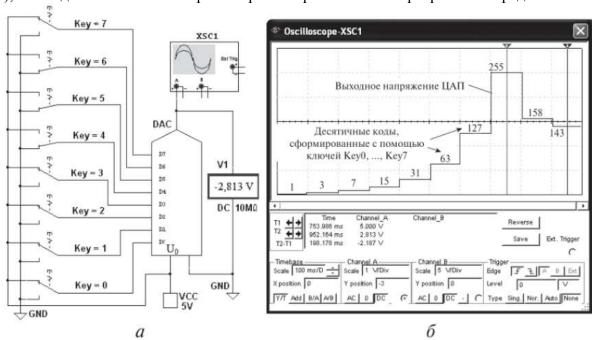

Входы дешифратора устроены так, что для отображения на индикаторе чисел 1, 2, 4 и 8 требуется нажатие лишь одной кнопки (на макете (рис.11) установлены тумблеры, соответствующие входам D0, D1, D2 и D3). Для отображения цифр требуется нажатие комбинации тумблеров, указанных в таблице 18.

Чтобы отобразить цифру "3" необходимо логическую единицу подать на вход D0 и D1. Если подать сигнал на D0 и D2, то отобразится цифра "5" (рис.11).

| Таблица 18 – | Таблица | истинности |

|--------------|---------|------------|

|--------------|---------|------------|

| Цифра | Входы |    |    |    |  |  |

|-------|-------|----|----|----|--|--|

|       | D3    | D2 | D1 | D0 |  |  |

| 0     | 0     | 0  | 0  | 0  |  |  |

| 1     | 0     | 0  | 0  | 1  |  |  |

| 2     | 0     | 0  | 1  | 0  |  |  |

| 3     | 0     | 0  | 1  | 1  |  |  |

| 4     | 0     | 1  | 0  | 0  |  |  |

| 5     | 0     | 1  | 0  | 1  |  |  |

| 6     | 0     | 1  | 1  | 0  |  |  |

| 7     | 0     | 1  | 1  | 1  |  |  |

| 8     | 1     | 0  | 0  | 0  |  |  |

| 9     | 1     | 0  | 0  | 1  |  |  |

Вспомогательными являются 1, 6 и 7-ой выводы микросхемы (S, M, К соответственно).

На схеме (рис.10) шестой вывод "М" заземлен (на минус питания) и на выходе микросхемы присутствует положительное напряжение для работы с индикатором с общим катодом. Если используется индикатор с общим анодом, то на шестой вывод следует подать единицу.

Если на 7-ой вывод "К" подать логическую единицу, то знак индикатора гасится, ноль разрешает индикацию. В схеме данный вывод заземлен (на минус питания).

На первый вывод дешифратора подана логическая единица (плюс питания), что позволяет отображать преобразованный код на индикатор. Но если подать на данный вывод (S) логический ноль, то входы перестанут принимать сигнал, а на индикаторе застынет текущий отображаемый знак.

Рисунок 11 – Демонстрация работы семисегментного индикатора

**Задание 1**. Нарисуйте семисегментный индикатор с точкой, 16-сегментный индикатор, светодиодную матрицу  $5 \times 7$ .

**Задание 2.** Определите параметры и характеристики микросхемы К176ИД2, укажите назначение выводов.

**Задание 3**. Зарисуйте электрическую принципиальную схему управления с описанием принципа действия.

#### Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если задания выполнены верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение заданий.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

# Тема 1.8. Цифровые комбинационные устройства (ЦКУ): арифметические устройства

# Практическое занятие №11 Анализ и синтез схем сумматоров

Цель: научиться выполнять анализ и синтез схем сумматоров.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

# Выполнение практической работы способствует формированию:

- ОК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

# Практические задания.

1. Используя таблицу истинности полусумматора, составьте временные диаграммы его работы.

| Входы |   | выходы |   |  |

|-------|---|--------|---|--|

| Α     | В | S      | P |  |

| 0     | 0 | 0      | 0 |  |

| 0     | 1 | 1      | 0 |  |

| 1     | 0 | 1      | 0 |  |

| 1     | 1 | 0      | 1 |  |

2. Постройте логическую схему, реализующую функцию полного одноразрядного сумматора, по логическим выражениям:

$$CR = cr \bullet a + cr \bullet b + a \bullet b$$

$$S = cr \cdot CR + a \cdot CR + b \cdot CR + cr \cdot a \cdot b$$

3. Используя таблицу истинности одноразрядного сумматора, составьте временные диаграммы его работы.

| Входы |   |    | выходы |    |  |

|-------|---|----|--------|----|--|

| A     | В | cr | S      | CR |  |

| 0     | 0 | 0  | 0      | 0  |  |

| 0     | 0 | 1  | 1      | 0  |  |

| 0     | 1 | 0  | 1      | 0  |  |

| 0     | 1 | 1  | 0      | 1  |  |

| 1     | 0 | 0  | 1      | 0  |  |

| 1     | 0 | 1  | 0      | 1  |  |

| 1     | 1 | 0  | 0      | 1  |  |

| 1     | 1 | 1  | 1      | 1  |  |

4. Используя логическую схему полусумматора (рис.1), в которой X и Y – слагаемые, Z1, Z2 – старший и младший разряды суммы, запишите логические уравнения  $Z1 = F_1(X,Y), Z2 = F_2(X,Y).$

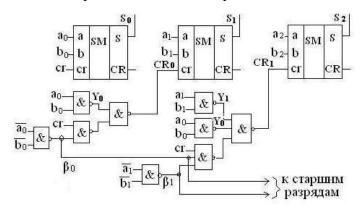

5. Из приведенной схемы сумматора (рис.2) с параллельным переносом запишите логические выражения для выработки сигналов переноса  $CR_0$  и  $CR_1$ .

Рисунок 2 - Сумматор с параллельным переносом

- 6. Используя схему умножителя (см. лекцию по теме 1.8.2), реализующего перемножение двух двоичных чисел: четырехразрядного  $A=A_4A_3A_2A_1$  и трехразрядного  $B=B_3B_2B_1$ , постройте схему для перемножения трехразрядного числа  $A=A_3A_2A_1$  и двухразрядного числа  $B=B_2B_1$  (на базе четырехразрядного сумматора).

- 7. Для одноразрядного компаратора постройте логическую схему по заданным выражениям, составьте таблицу истинности и нарисуйте временные диаграммы его работы (а и b входные сигналы):

$$y(a > b) = a\overline{b}$$

$$y(a < b) = \overline{ab}$$

$$y(a = b) = a\overline{b} \vee \overline{ab}$$

- 8. Для ИМС 133ИМ2, 533ИМ5, 533СП1:

- определите параметры микросхем и заполните таблицу 1

- зарисуйте условно-графическое обозначение микросхем с основными выводами;

- зарисуйте тип корпуса и запишите его характеристики.

Таблица 1 - Параметры микросхем арифметических устройств

| Маркир<br>овка<br>ИМС | Тип<br>логики | Функциональное назначение | Тип корпуса по ГОСТ | Потребляемая мощность, мВт | Напряжение питания, В | Время задержки, t <sub>зал</sub> , нс | Коэффициент<br>разветвления, К <sub>раз</sub> | Максимальная частота<br>входного сигнала, МГц |

|-----------------------|---------------|---------------------------|---------------------|----------------------------|-----------------------|---------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 133ИМ2                |               |                           |                     |                            |                       |                                       |                                               |                                               |

| 533ИМ5                |               |                           |                     |                            |                       |                                       |                                               |                                               |

| 533СП1                |               |                           |                     |                            |                       |                                       |                                               |                                               |

# Форма представления результата:

Отчет по работе должен содержать:

- 1) наименование работы и цель работы;

- 2) результаты работы;

- 3) выводы по работе.

#### Критерии оценки:

Оценка «отлично» ставится, если задания выполнены верно.

Оценка «хорошо» ставится, если была допущена одна или две ошибки.

Оценка «удовлетворительно» ставится, если приведено неполное выполнение заданий.

Оценка «неудовлетворительно» ставится, если задание не выполнено.

# Тема 1.9. ИМС запоминающих устройств Практическое занятие №12 Проектирование блока ОЗУ

Цель: научиться выполнять анализ и синтез схем сумматоров.

# Выполнив работу, Вы будете:

уметь:

- выполнять анализ и синтез схем цифровых устройств;

- разрабатывать схемы цифровых устройств на основе интегральных схем разной степени интеграции.

#### Выполнение практической работы способствует формированию:

- OК 01. Выбирать способы решения задач профессиональной деятельности применительно к различным контекстам;

- OК 05 Осуществлять устную и письменную коммуникацию на государственном языке Российской Федерации с учетом особенностей социального и культурного контекста;

- ОК 09 Пользоваться профессиональной документацией на государственном и иностранном языках.

- ПК 1.1. Анализировать требования технического задания на проектирование цифровых систем.

- ПК 1.2. Разрабатывать схемы электронных устройств на основе интегральных схем разной степени интеграции в соответствии с техническим заданием.

**Материальное обеспечение:** для проведения практической работы требуется наличие специальной литературы, интернет-ресурсы.

#### Краткие теоретические сведения

Проектирование блока ОЗУ заданной емкости и разрядности рассмотрено в примере.

**Пример.** Выполните проектирование блока ОЗУ на базе ИМС К537РУ13 емкостью 2К 8-ми разрядных слов.

#### Решение

Рассчитываемый блок ОЗУ может применяться в локальной микропроцессорной системе управления для хранения результатов измерения (например, датчиков).

Применение стандартных модулей ОЗУ для тех же целей не всегда возможно и целесообразно, т.к. могут отсутствовать стандартные разъемы для установки и подключения этих модулей в микропроцессорных системах (например, промышленных контроллерах, выполняющих функции слежения, сбора данных и управления), а, кроме того, ОЗУ большой емкости и разрядности могут не требоваться, если необходимо сохранить небольшое количество данных. Поэтому, в таких случаях, приходится производить расчет ОЗУ заданной емкости и разрядности.

Так как, микропроцессорная система выполняется по модульному принципу, то, заменяя хотя бы один блок можно получить систему с новыми параметрами. Поэтому для одной и той же микропроцессорной системы возможно применение нескольких съемных блоков ОЗУ различной

емкости и разрядности. Однако для этого требуется соблюсти некоторые стандарты: все разъемы на печатной плате выполняются с одной стороны и соответствуют разъемам микропроцессорной системы (8 линий данных, 16 линий адреса и линии управления).

Выбор ИМС для блока ОЗУ.

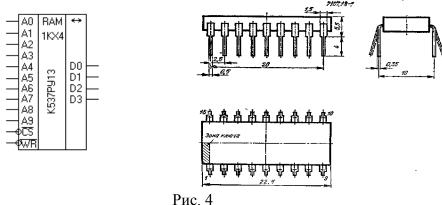

Микросхемы К537РУ13 представляют собой статическое асинхронное запоминающее устройство емкостью 4К (1024 слова по 4разряда).

На рис.4 приведено УГО и цоколевка выводов ИМС К537РУ13. На рис. 5 приведено изображение корпуса ИМС (корпус типа 2107.18-1).

Таблица 2. Назначение выводов К537РУ13

| Tuomiqu 2. Tuoma territo bbibogob 1005/1010 |             |            |                     |  |  |

|---------------------------------------------|-------------|------------|---------------------|--|--|

| Вывод                                       | Обозначение | Тип вывода | Назначение          |  |  |

| 1-4, 17-15, 5-7                             | $A_0 - A_9$ | Bx         | Адресная шина       |  |  |

| 11 - 14                                     | $D_1 - D_4$ | Вх/Вых     | Информационная шина |  |  |

| 8                                           | CS          | Bx         | Выбор кристалла     |  |  |

| 10                                          | WR/RD       | Bx         | Запись/чтение       |  |  |

| 18                                          | $U_{CC}$    | -          | Напряжение питания  |  |  |

| 9                                           | GND         | -          | Общий провод        |  |  |

Электрические параметры К537РУ13

| Номинальное напряжение питания, В                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Напряжение питания в режиме хранения, В≥2                                                                                                                                                                |

| Выходное напряжение низкого уровня, В≤0,4                                                                                                                                                                |

| Выходное напряжение высокого уровня, В:                                                                                                                                                                  |

| при I <sub>1 вых</sub> = -2мА, U <sub>п</sub> =5В············                                                                                                                                            |

| при $I_{1 \text{ вых}} = -0.4 \text{мA}, U_{\text{п}} = 5 \text{B} \cdots \cdots$ |

| Ток потребления в режиме хранения при U <sub>п</sub> =5В,мА··· ≤5                                                                                                                                        |

| Ток утечки низкого уровня на выходе, мкА   -10                                                                                                                                                           |

| Ток утечки высокого уровня на выходе, мкА······                                                                                                                                                          |

| Ток утечки низкого уровня на входе, мкА······                                                                                                                                                            |

| Ток утечки высокого уровня на входе, мкА······ 1                                                                                                                                                         |

| Входное напряжение низкого уровня, В0,30,8                                                                                                                                                               |

| Входное напряжение высокого уровня, В                                                                                                                                                                    |

| Выходной ток низкого уровня, мА4                                                                                                                                                                         |

| Выходной ток высокого уровня, мА2                                                                                                                                                                        |

| Емкость нагрузки, пФ                                                                                                                                                                                     |

| Входная ёмкость, пФ                                                                                                                                                                                      |

| Выходная ёмкость, пФ                                                                                                                                                                                     |

| Входной ток низкого уровня, мА                                                                                                                                                                           |

| Входной ток высокого уровня, мА                                                                                                                                                                          |

| Способы соединения ИМС ОЗУ                                                                                                                                                                               |

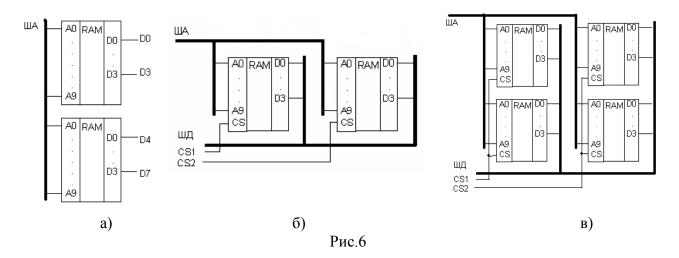

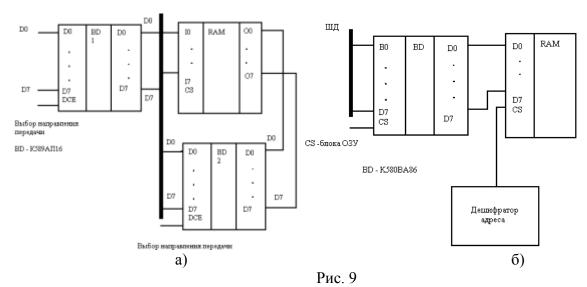

При проектировании блока ОЗУ используются следующие способы соединения ИМС ОЗУ:

#### 1. Увеличение разрядности.

Увеличение разрядности производится за счет объединения адресных входов ИМС (рис.6, а). При подаче адреса ячейки во всех ИМС выбираются ячейки с одним и тем же адресом, при этом старшие разряды слова хранятся в одной ИМС, а младшие — в другой. Одно слово можно разделить не только на две ИМС, а и на другое количество для обеспечения требуемой разрядности.

#### 2. Увеличение емкости

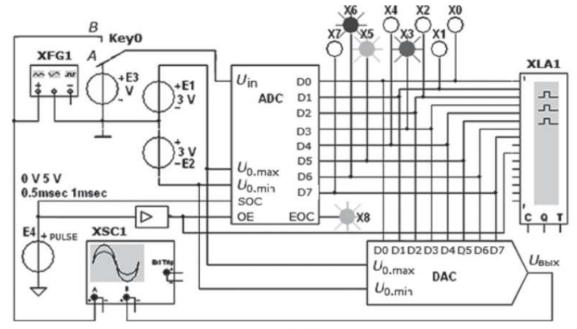

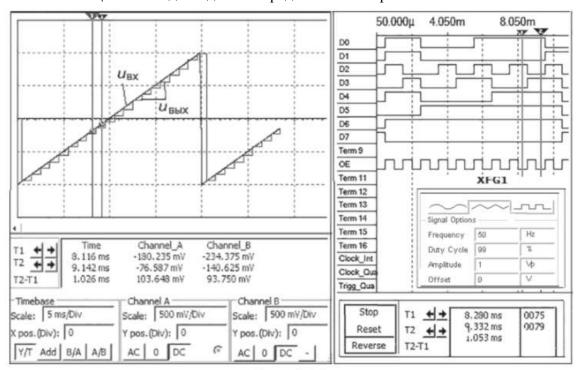

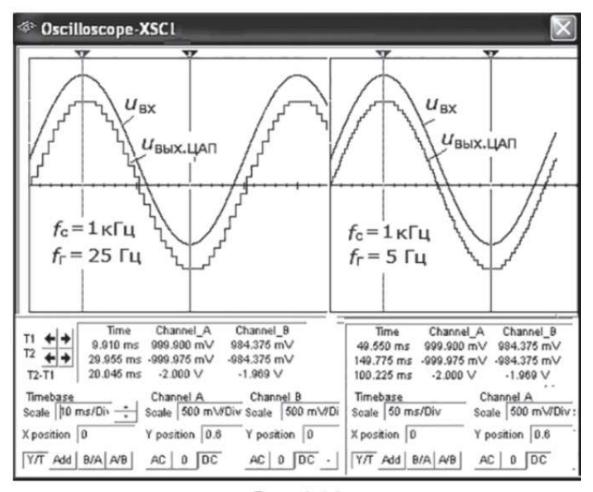

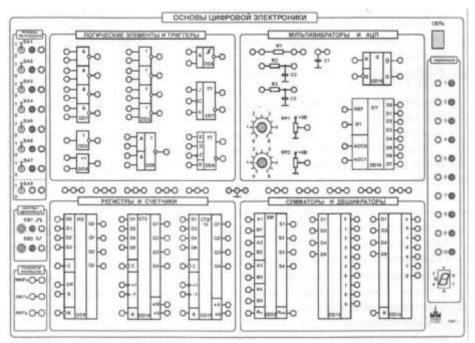

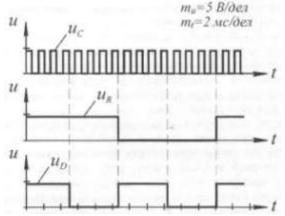

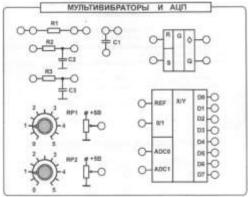

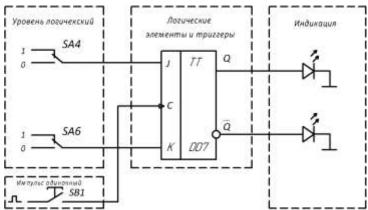

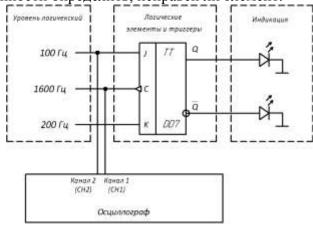

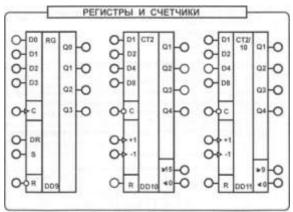

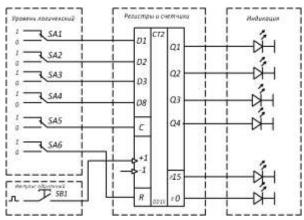

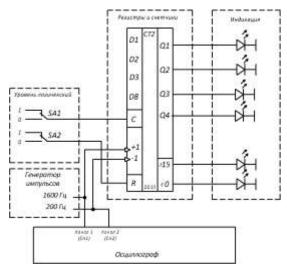

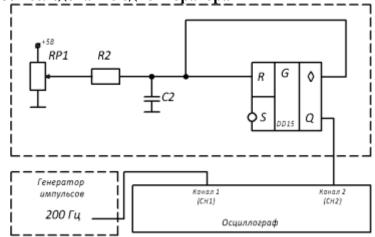

Для увеличения емкости информационные входы-выходы ИМС объединяются (рис.6, б). Если требуется увеличить и емкость, и разрядность, то объединяются и адресные, и информационные выводы ИМС. Оставшиеся старшие разряды шины адреса используются для выбора групп ИМС (рис.6, в).